I’m sure many of you have read Andy Grove’s classic book, “Only the Paranoid Survive”. Let’s now apply the principles in Grove’s book to the foundry industry. If you were Morris Chang and had 50% market share in the foundry industry, which competitor of yours would you be “paranoid” about?

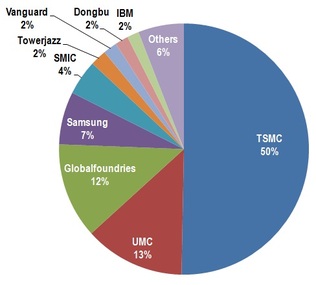

Fig. 1 shows the foundry landscape at the end of 2011. Many competitors show up: there’s Globalfoundries with its plentiful oil money, UMC with its excellent customer service and high yields and SMIC with its Chinese government backing. But, to me, Samsung is undoubtedly the biggest threat to TSMC, even though its foundry market share today is just 7%. Let me explain why...

Economies of Scale due to Memory Business

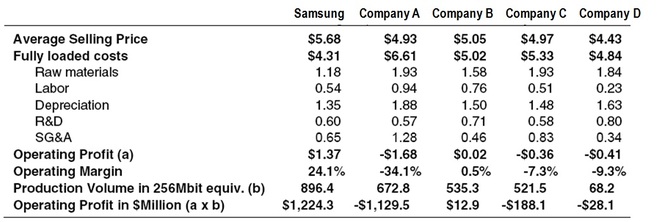

Semiconductor manufacturing costs are heavily dependent on economies of scale. Fig. 2 [1][2], which is an estimate of DRAM costs and selling prices in 2003, illustrates this point. The highest volume producer, Samsung, has the lowest raw material costs in Fig. 2. The same goes for semiconductor equipment purchases. A higher volume producer gets a lower price per tool. You’ll notice the highest volume producer (Samsung) has the lowest depreciation cost in Fig. 2.

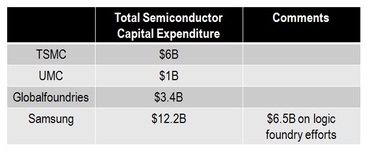

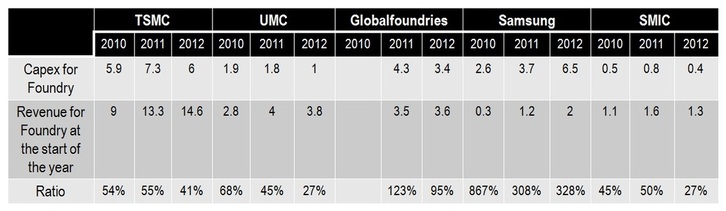

What does this mean for the foundry industry? Well, TSMC, since it has 50% market share, should benefit from economies of scale and build a lead over its rivals, right? That certainly gives TSMC an advantage over UMC and Globalfoundries, but doesn’t work with Samsung. Why? Because Samsung owns a huge chunk of the world’s memory business (~40%). It buys tools and raw materials in huge volumes for those markets, and you use pretty similar tools and raw materials for logic foundry manufacturing. Fig. 3 illustrates that Samsung’s capital expenditure for tools in 2012 is actually double that of TSMC. Samsung might therefore have lower raw material costs and depreciation costs than TSMC.

Yield improvement methodologies

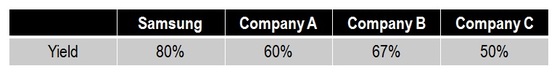

Samsung has a great set of yield improvement methodologies developed over its years in the competitive memory industry. Fig. 5 [2] illustrates yields of different DRAM manufacturers in 2003. You’ll notice Samsung has, by far, the best yields. Based on this data and Samsung’s reputation for high-yield memory products, you would expect Samsung to get good yields in the logic foundry business. They seem to be delivering on that front. I hear from industry contacts that Samsung is the only manufacturer getting reasonable yields for gate-first high k metal gate products at 28nm.

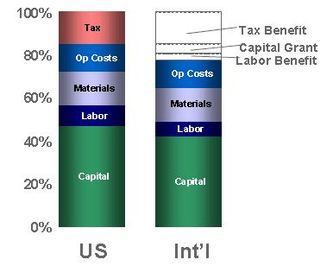

Low cost fabs

In cost sensitive markets such as memory and foundries, the location of a fab makes a difference. Fig. 5 [3] shows a chart from the US National Academy of Engineering which reveals that fab costs in the US are ~25% higher than fab costs in the Far East. Some of TSMC’s competitors have fabs in Europe and the US, but Samsung is building a good portion of its capacity in Korea (they do have one facility in Texas though). The fab cost advantage TSMC has over its other competitors doesn’t necessarily exist with Samsung.

Sensible partnership strategy

One of the barriers to entry for the foundry business is availability of Intellectual property (IP) blocks and CAD tool support. Intel, which is looking to enter the foundry business, has difficulties with this, since IP blocks haven’t been developed for its technologies yet. SoC makers today show a marked preference for foundries offering competitive IP blocks at low prices.

When Samsung entered the foundry industry, it addressed this issue by joining the IBM alliance, and so its customers could use IP blocks developed for the IBM alliance. Samsung did not have much experience developing logic technologies either, and the alliance helped Samsung learn from existing players in the logic business such as IBM and Globalfoundries. In spite of having a similar technology offering to Globalfoundries and IBM, Samsung retains an advantage over these competitors since it is better at ramping up yields and because it has low cost fabs.

R&D costs for next-generation logic technologies are $1-2 billion today. Sharing the cost with IBM and Globalfoundries gives Samsung a R&D cost advantage over companies such as TSMC and UMC which develop new technologies alone.

Ability to fund large capital expenditures

TSMC, UMC, Globalfoundries and SMIC derive almost all their sales from the foundry industry. This limits the amount of capacity they can add every year, since their balance sheets place restrictions on maximum cap-ex to revenue ratio (Globalfoundries is an exception here due to its oil money). Samsung, on the other hand, is a diversified company that sells everything from TVs to DRAM to NAND flash to cell phones. It routinely takes profits from other divisions and invests it in the logic foundry industry. Fig. 6 [4] illustrates this trend. Samsung’s capex to revenue ratio for its foundry business is way higher than anyone else. This added capacity is helping Samsung’s foundry business grow rapidly – notice how Samsung’s froundry revenues increased almost 7x between 2010 and 2012. Samsung used this “capacity-add-like-there-is-no-tomorrow” strategy to become our industry’s biggest DRAM producer, so the foundry folks had better watch out!

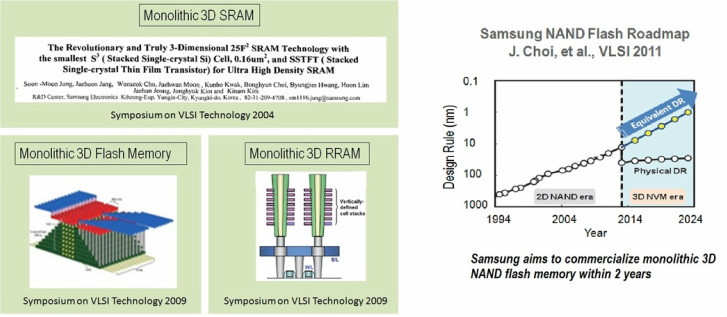

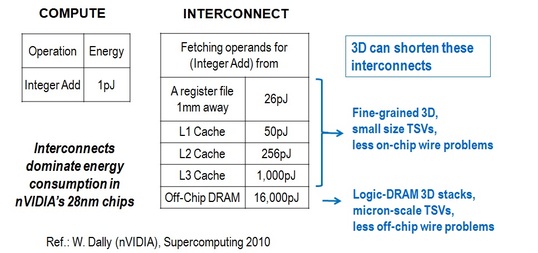

Proven Research Expertise

If you talk with engineering folks in our industry and ask them which companies do the best research, you will find Samsung near the top of the list. Let me illustrate Samsung’s research capabilities using Monolithic 3D as an example. They started working on the technology almost 10 years back, and have developed monolithic 3D technologies for NAND flash, SRAM and resistive memories. In addition, their roadmap calls for commercialization of Monolithic 3D NAND flash memories within 2 years. Check out Fig. 7. This is some of the best work I’ve seen on monolithic 3D so far. This phenomenal research capability will help Samsung make strides in the logic space.

Caveat

While the above capabilities of Samsung threaten TSMC in the long term, there are stormy clouds looming for Samsung in the short term. Apple, which accounts for more than 75% of Samsung’s foundry revenues [4] today, is flirting with TSMC due to its increasingly litigious competition with Samsung in the mobile space. If TSMC executes well and takes this business away from Samsung, it could be a big blow to Samsung’s ambitions.

To summarize

I explained why I believe Morris Chang will consider Samsung his biggest competitor in the long-term. The economies of scale Samsung has due to its memory business could help its logic operations. Samsung’s superb yield ramp capabilities and low cost Korean fabs are another key asset. Probably the biggest weapon Samsung has is its conglomerate (chaebol) structure, which allows it to make huge capital investments and grow rapidly.

At the start of this write-up, I talked about how Morris Chang has grown TSMC the way Andy Grove grew Intel. One of Andy Grove’s strengths was that he recognized Intel’s biggest challenges, and channelized his “paranoia” and limitless energy into finding counter-measures. What can Morris Chang do to deal with “the Samsung challenge”? In a future blog post, I will describe strategies for this... stay tuned!

- Post by Deepak Sekar

RSS Feed

RSS Feed