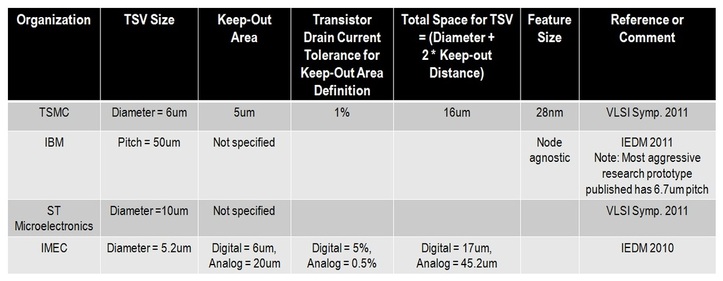

Many companies such as TSMC, IBM, ST Microelectronics and others have announced 3D Through-Silicon Via (TSV) technologies. In Figure 1, I've summarized key aspects of these technologies. You'll notice TSV sizes are in the micron range, while feature sizes are in the nm range.

In case you're wondering what I mean by keep-out zones in Figure 1: TSVs are typically constructed of copper, which has co-efficient of thermal expansion (CTE) 17ppm/K. This is very different from the CTE of silicon (2.3 ppm/K). Due to this, TSVs introduce stress on transistors placed close to them, impacting transistor performance. To avoid these issues, keep-out zones exist around TSVs. Transistors are not placed within these keep-out zones.

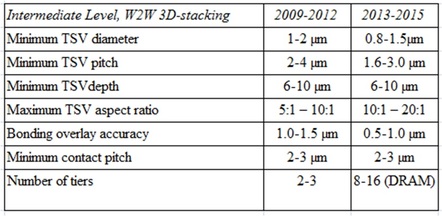

- Wafer thinning - The best aspect ratio possible for TSV manufacturing is around 10:1 right now. So, if you have to make a 1um diameter TSV, you will need to thin a 775um thick wafer to 10um +/- 1um, which is immensely challenging, especially considering throughput requirements. Many companies therefore make their lives easier by thinning 775um wafers to 50um +/- 5um, which gives 5um diameter TSVs for 10:1 aspect ratio. Manufacturing throughput is also better in this case. Of course, this comes at the expense of TSV size.

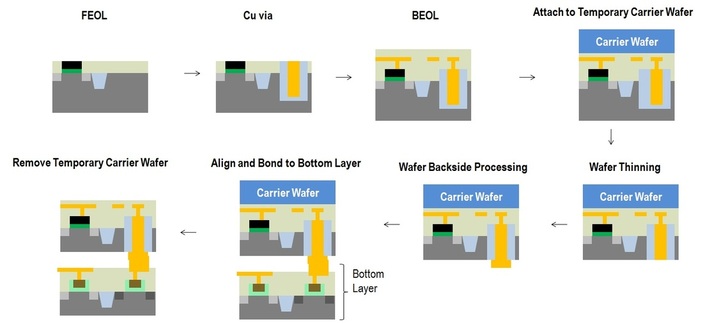

- Alignment and bonding - During the "align and bond to bottom layer" step in Figure 3, several issues arise. Co-efficient of thermal expansion between layers being bonded is often different, causing misalignment when temperature changes during bonding. Processed wafers that are being bonded may have different bow, introducing more misalignment. The nature of the substrate (eg. transparent or opaque) can change alignment accuracy too. As mentioned in Figure 2, bonding overlay accuracy is around 1-1.5um for state-of-the-art technologies today.

- Post by Deepak Sekar

RSS Feed

RSS Feed