|

We have a guest contribution from Zvi Or-Bach, the President and CEO of MonolithIC 3D Inc.

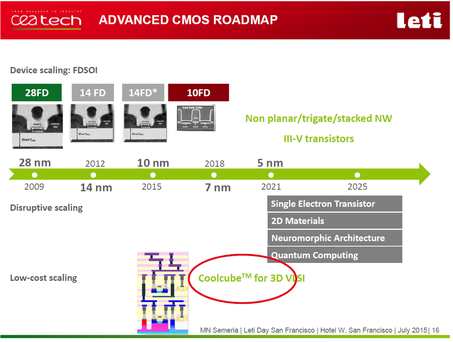

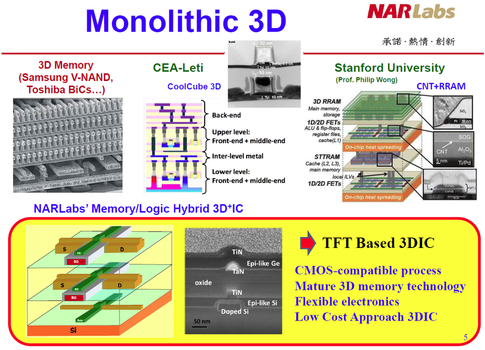

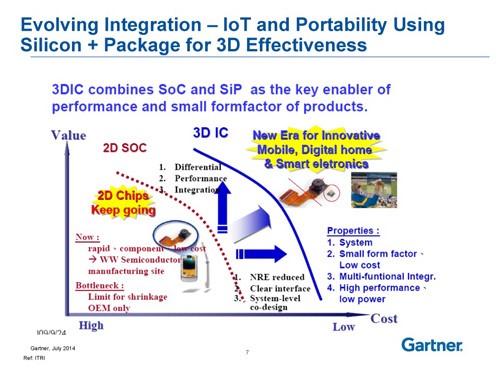

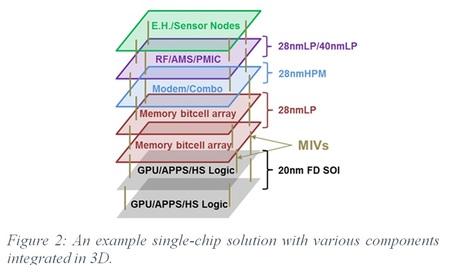

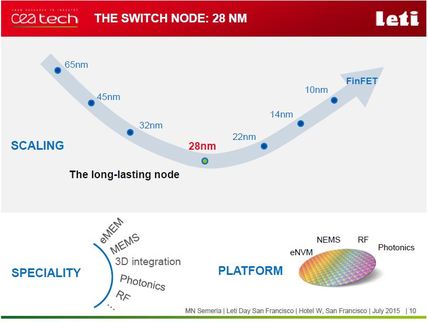

We were invited to join a panel session titled: "Monolithic 3D: Will it Happen and if so..." at IEEE 3D-Test Workshop Oct. 9th, 2015. So we are happy to see monolithic 3D on the title, but then the title also suggests that the industry is wondering is it real or is it a pipe dream. The doubts are in opposition to companies such as Qualcomm who strongly advocate it, and the support CAE which Leti, in collaboration with ST Micron and IBM,are presenting monolithic 3D as the "low-cost scaling" for 2018. See chart below from July 2015 Leti Day. |

Game-Changing 2.0 @ IEEE S3S

In short the most comprehensive technical event on the emerging monolithic 3D technologies.

Yet – the question “Monolithic 3D: Will it Happen…” is still being asked.

The concerns are that the leading edge vendors are too busy these days still with dimensional scaling and if anything else could be done it seems that FD-SOI would be it; while trailing edge fabs, are in most cases, avoiding any major transistor process development. The recent failure of Suvolta could be an indication of this reality.

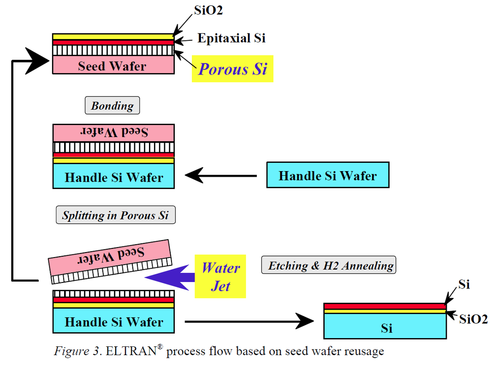

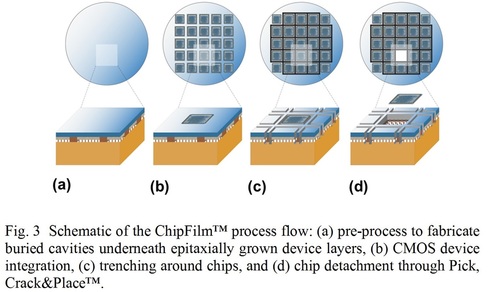

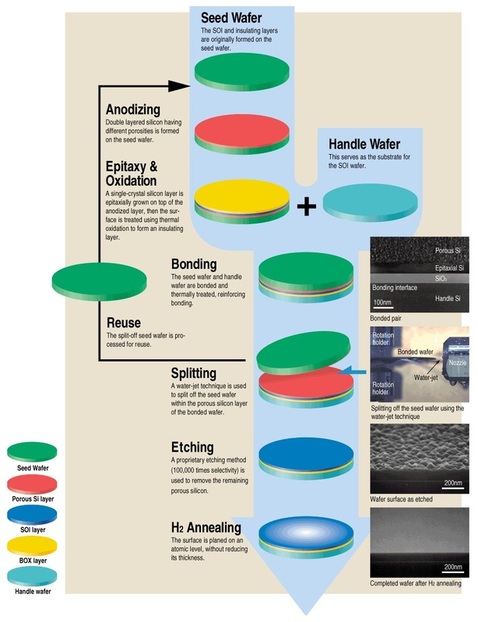

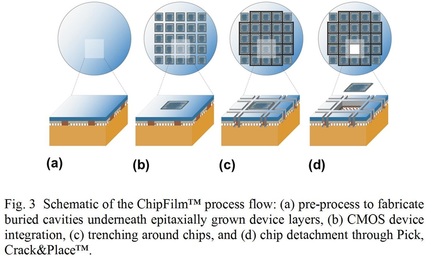

Here comes Game-Changing 2.0. A major technology innovation to be unveiled on Wednesday by MonolithIC 3D in a paper titled: “Modified ELTRAN® - A Game Changer for Monolithic 3D”. This paper will present a novel use of the ELTRAN® process developed by Canon Inc. about 20 years ago primarily for SOI applications. Using ELTRAN (Epi. Layer Transfer) techniques, a substrate could be prepared enabling any fab to simply integrate a monolithic 3D device without the need to change the current frontline fab process. This flow is further simplified and could be integrated with the game changing monolithic 3D flow introduced last year which leverages the emerging precision bonders, such as EVG’s Gemini® XT FB. This flow provides a natural path for product innovation and an unparalleled competitive edge. In addition, this game-changer breakthrough offers a very cost competitive flow. The following chart illustrates the original use of ELTRAN process for the fabrication of SOI wafers:

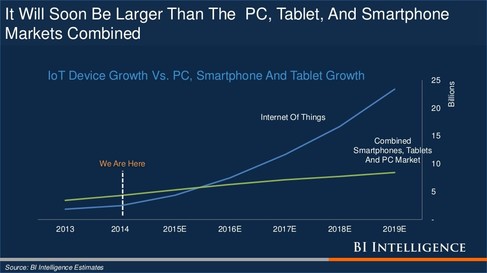

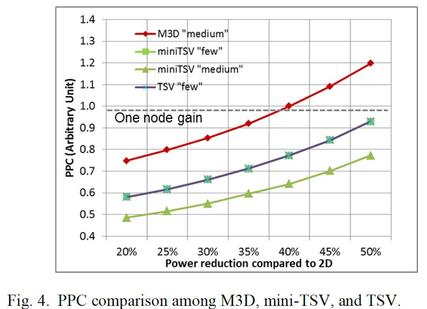

The semiconductor industry are bifurcating these days into one a segment that follows aggressive scaling for few super-value applications supported by very few vendors, while the bulk of the industry is enhancing old fabs while targeting the main stream applications and the emerging IoT opportunities. Further enhancing these older fabs with monolithic 3D would be a most effective return on investment. As indicate by the CEA slide above – “low cost scaling” and by a paper to be presented by Global Foundries showing monolithic 3D provides Power-Performance-Area (PPA) equivalent to dimension scaling at fraction of the cost. The Game-Changing 2.0, mean that without need for major process R&D efforts or new equipment the path for 3D scaling is now open with enormous advantages for IoT. And accordingly my answer to the above question is encompassed in the title of the invited talk prior to the panel “Monolithic 3D is Already Here – the 3D NAND – and Now it would be Easy to Adapt it for Logic”

In addition the other division – SOI and SubVt provide good complementing technology updates for the power performance objectives that are so important for these emerging markets. So do come to the S3S and enjoy unique key technologies update with the great wine and country pleasures of Sonoma Valley.

RSS Feed

RSS Feed