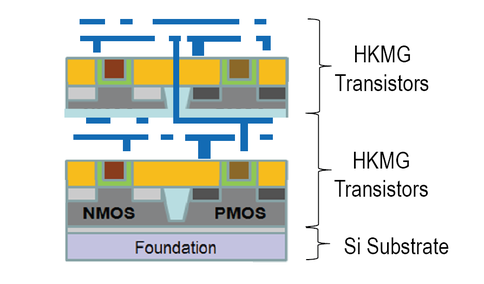

Monolithic 3D High Performance (HKMG) Transistors

Follow link for presentation on: Detailed HKMG flow.

TechnologyThe monolithic 3D IC technology is applied to produce monolithically stacked high performance High-k Metal Gate (HKMG) devices, the world’s most advanced production transistors.

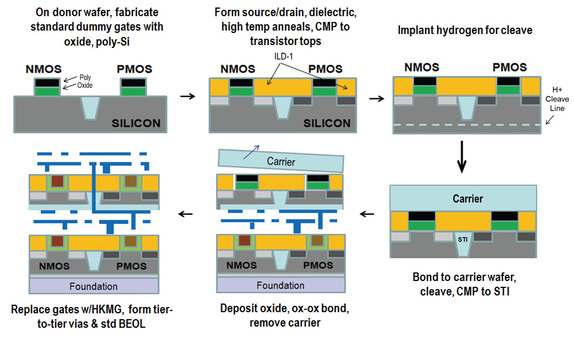

3D Monolithic State-of-the-Art transistors are formed with ion-cut applied to a gate-last process, combined with a low temperature face-up layer transfer, repeating layouts, and an innovative inter-layer via (ILV) alignment scheme. Monolithic 3D IC provides a path to reduce logic, SOC, and memory costs without investing in expensive scaling down. |

Benefits

|

HKMG 3D Flow

Create a logic layer with any transistor that uses a replacement-gate process. Innovative alignment schemes, combined with repeating layouts, obtain sub-50nm, and hence dense, through-silicon electrical connections.

Leveraging a mature technology (wafer bonding and ion-cleaving) that has been the dominant SOI wafer production method for over two decades.

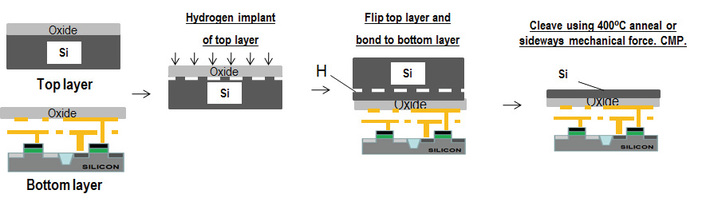

Innovate and create multiple thin (10s – 100s nanometer scale) layers of virtually defect free Silicon by utilizing low temperature (<400C) bond and cleave techniques, and place on top of active transistor circuitry. Benefit from a rich layer-to-layer interconnection density.