Monolithic 3D eDRAM on Logic

Follow link for presentation on: Logic + eDRAM on top

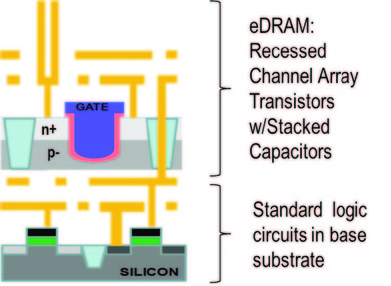

TechnologyMonolithic 3D IC technology is applied to producing monolithically stacked low leakage Recessed Channel Array Transistors (RCATs) with stacked capacitors (eDRAM) on top of logic.

Enjoy the cost savings of a footprint reduction of 75% and an active silicon area reduction of 50% by monolithically stacking the eDRAM on top of logic. The eDRAM and logic device layers can be independently optimized, no more wasting 10 metal layers on DRAM die area. Enables the use of the 3 times more area efficient DRAM instead of SRAM for memory. RCATs can be used for memory cells and decoder logic, and an independent refresh port allows reduced voltage and power. Short wires and close proximity of the eDRAM to logic provides maximum performance. |

Benefits

|

eDRAM on logic flow

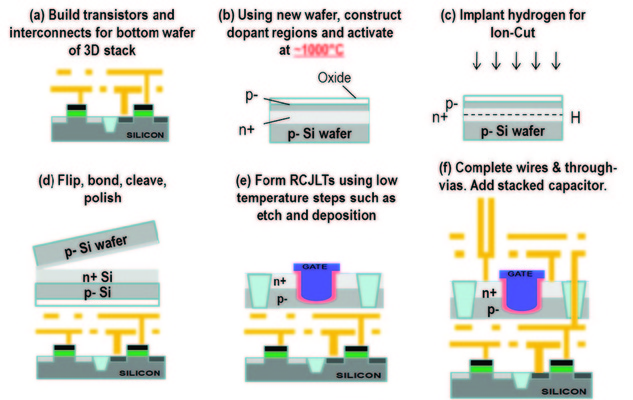

Create a layer of Recessed ChAnnel Junction-Less Transistors (RCATs), commonly used in DRAMs, by activating dopants at ~1000oC before wafer bonding to the CMOS substrate and cleaving, thereby leaving a very thin doped stack layer from which transistors are completed, utilizing less than 400oC etch and deposition processes. Add stacked caps.

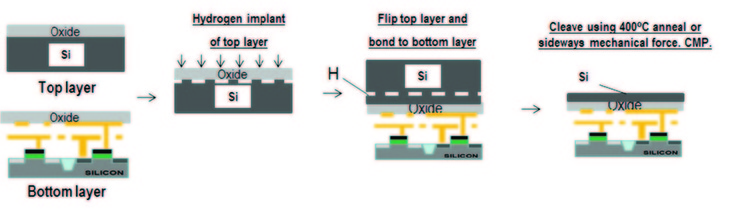

Leveraging a mature technology (wafer bonding and ion-cleaving) that has been the dominant SOI wafer production method for over two decades.

Innovate and create multiple thin (10s – 100s nanometer scale) layers of virtually defect free Silicon by utilizing low temperature (<400oC) bond and cleave techniques, and place on top of active transistor circuitry. Benefit from a rich layer-to-layer interconnection density.