Accordingly the industry developed a 3D IC technology based on TSV (Thru Silicon Via) where each strata (wafer) could be independently processed, then after thinning at least one wafer, place in a 3D configuration, and then connect the strata with TSV using a low temperature (<400°C) process. This independent (parallel) processing has its own advantages; however, the use of thick layers (>50 µm) greatly limits the vertical connectivity, requires development of all new processing flows, and is still too expensive for broad market adoption. On the other hand, monolithic 3D IC provides a 10,000x better vertical connectivity and would bring many additional benefits as was recently presented in the IEEE 3D IC conference.

The semiconductor industry is always on the move and new technologies are constantly being introduced making changes the only thing that is constant. For the most part dimensional scaling has been associated with introducing new materials and challenges, thereby making process steps that were once easy far more complex and difficult. But not so in respect to monolithic 3D IC.

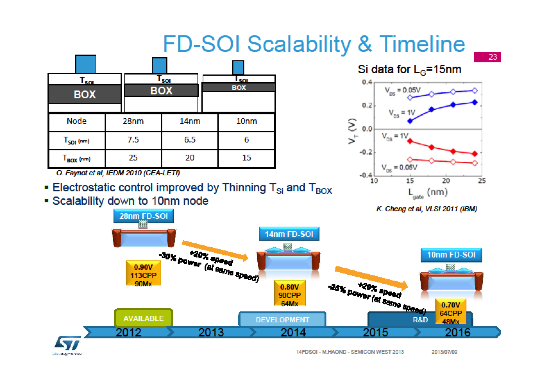

The amount of silicon associated with a transistor structure was measured in microns in the early days of the IC industry and has now scaled down to the hundreds and the tens of nano-meters. The new generation of advanced transistors have thicknesses in nanometers as is illustrated in the following ST Micro slide.

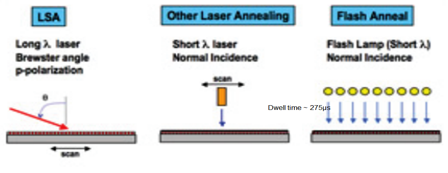

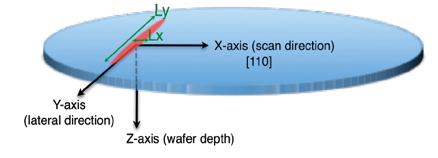

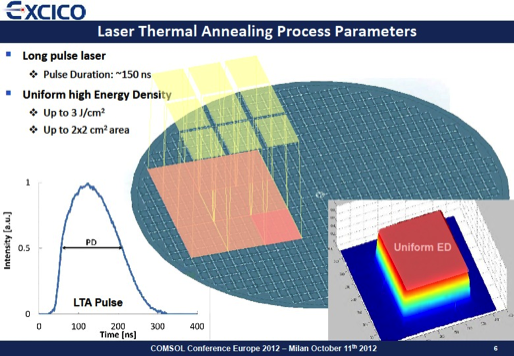

And unlike furnace heating or RTP annealing, with laser annealing the heat is coming from the top and directed only on small part of the wafer as illustrated below.

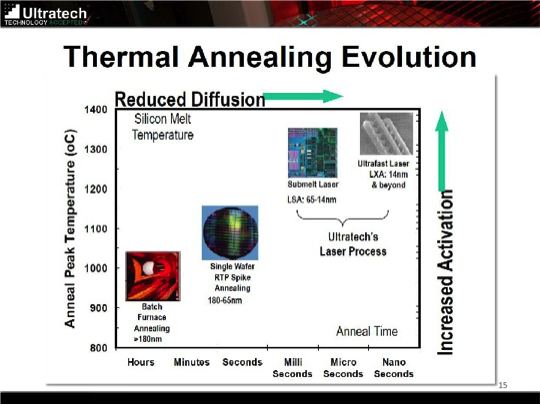

These trends help make it practical to protect the first strata interconnect from the high temperature process required for the second strata transistor formation. As the high temperature is on small amount of silicon for a very short time and for a small part of the wafer, the total amount of thermal energy required for activation/annealing is now very small.

One of the three most newsworthy topics and papers included in the 2013 IEDM Tip Sheet for the “Advances in CMOS Technology & Future Scaling Possibilities” track was a monolithic 3D chip fabricated using a laser (reported by Solid State magazine “Monolithic 3D chip fabricated without TSVs“). Quoting: “To build the device layers, the researchers deposited amorphous silicon and crystallized it with laser pulses. They then used a novel low-temperature chemical mechanical planarization (CMP) technique to thin and planarize the silicon, enabling the fabrication of ultrathin, ultraflat devices. The monolithic 3D architecture demonstrated high performance – 3-ps logic circuits, 1-T 500ns nonvolatile memories and 6T SRAMs with low noise and small footprints, making it potentially suitable for compact, energy-efficient mobile products.”

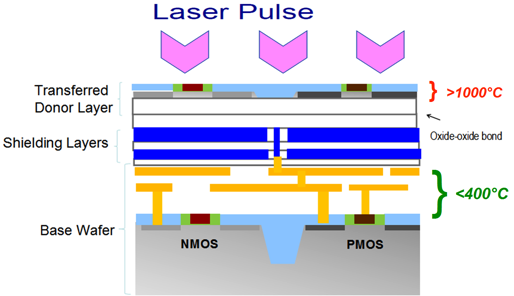

Furthermore, in last two weeks we presented in the IEEE 3D IC and IEEE S3S conferences an alternative simulation based work. We suggested to use a smart-cut® for the formation of the second strata (and not amorphous silicon crystallization) with innovative shielding layers to protect the first strata interconnect, as illustrated below.

Summary: In short, dimensional scaling is becoming harder and yet it makes monolithic 3D easier. We should be able to keep scaling one way or the other (or even both), and keep enjoying the benefits.

Note: smart-cut® s a register TM of Soitec

RSS Feed

RSS Feed