Dimension Scaling and the SRAM Bit-Cell

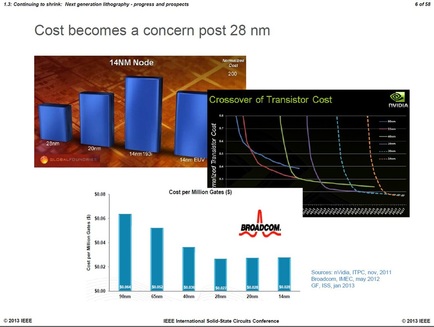

As widely reported Martin van den Brink ASML Executive VP & CTO articulate that without EUV cost of logic transistors is most likely go up with scaling as was illustrated by his following slide:

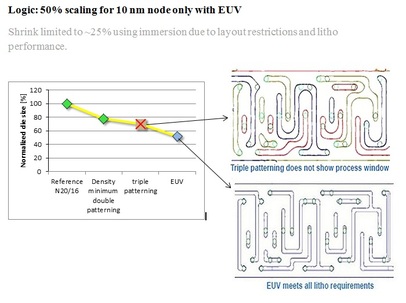

The real interesting slid presented by van den Brink is the following:

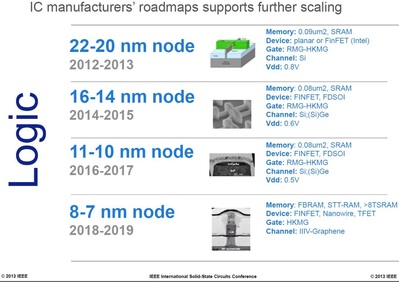

Accordingly the SRAM bit-cell size might not be reduced from 20nm to 10 nm and might even get larger at 7nm as it may need more than 8 transistors.

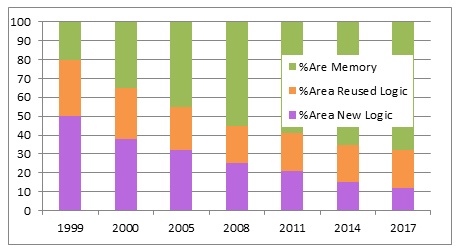

Modern logic devices needs significant amount of embedded SRAM in fact more than 50% of the logic device area is allocated for these SRAM as illustrated by the following chart of Semico (June, 2010)

As SRAM bit scale is becoming less than 50% we had seen in the past, the end device scaling cost could be even more disappointing than the transistor or gate cost illustrations above.

Well aware of this IBM had been promoting their embedded DRAM solution for years. In the recent Common Platform Forum Dr. Gary Patton, VP, IBM Semiconductor R& D Center, was very pleased to share that at 32nm product line IBM use of the embedded DRAM gave them the equivalent of process node benefits. Yet as of now most other vendors had not adapted the eDRAM due to process complexity it adds to the logic process. It fair to assume that the appetite for eDRAM will not grow with dimension scaling as the DRAM capacitor will be very hard to scale, the extra power for DRAM is not available and the cost of advance process development is too high to add in extra complexity.

Accordingly we could learn from these recent ISSCC that dimension scaling is facing the cost challenges we were aware of before plus one that we have might been less aware of but could hit us both on cost and on power due to the incompatibility of the 6T SRAM bit-cell with scaling.

As we suggested before, now that monolithic 3D is practical, we could advance and maintain Moore's Law by augmenting dimension scaling with 3D IC scaling, allowing depreciation and advance engineering to bring down costs and improvements to power and performance. And additional option is to replace the 6T SRAM bit-cell with the 1T - two stable states floating body memory cell invented by Zeno Semiconductor. The Zeno bit-cell is getting better with scaling save ~80% of the silicon area and require far less power, yet it provides two stable memory states, and would work on existing logic process.

RSS Feed

RSS Feed