Progress in

- 3D - TSV technology, and

- EUV

1. As the advanced node progresses to smaller and smaller feature size we are getting closer to the "end of the road map" or the "end of Moore's law".

Going to EUV does alleviate some of the problems related to the current solution of double patterning (or quadruple in the future assuming, EUV doesn't come to fruition soon enough).

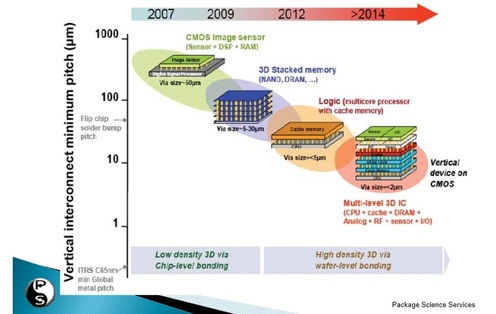

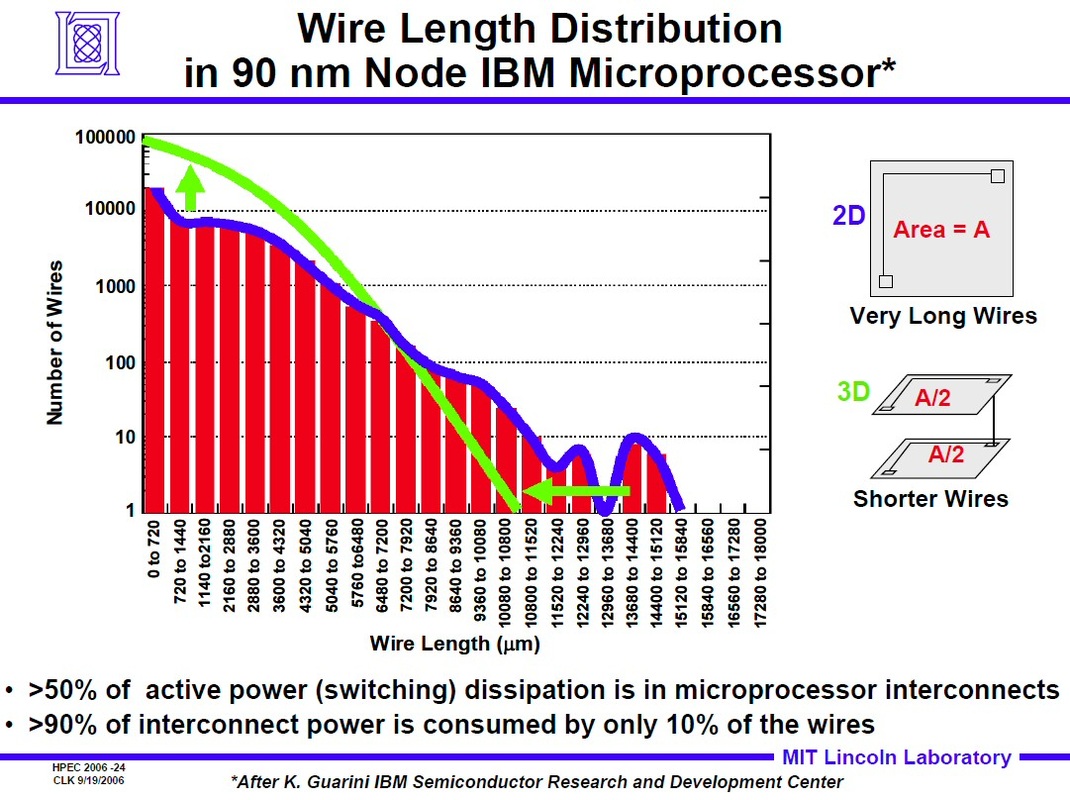

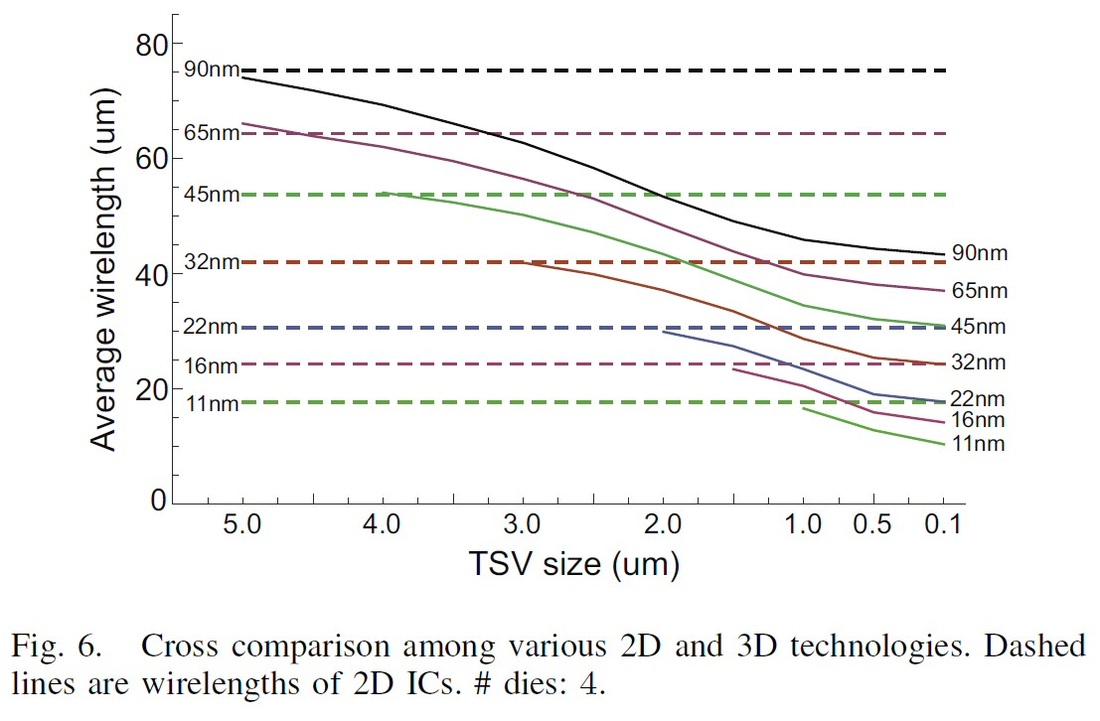

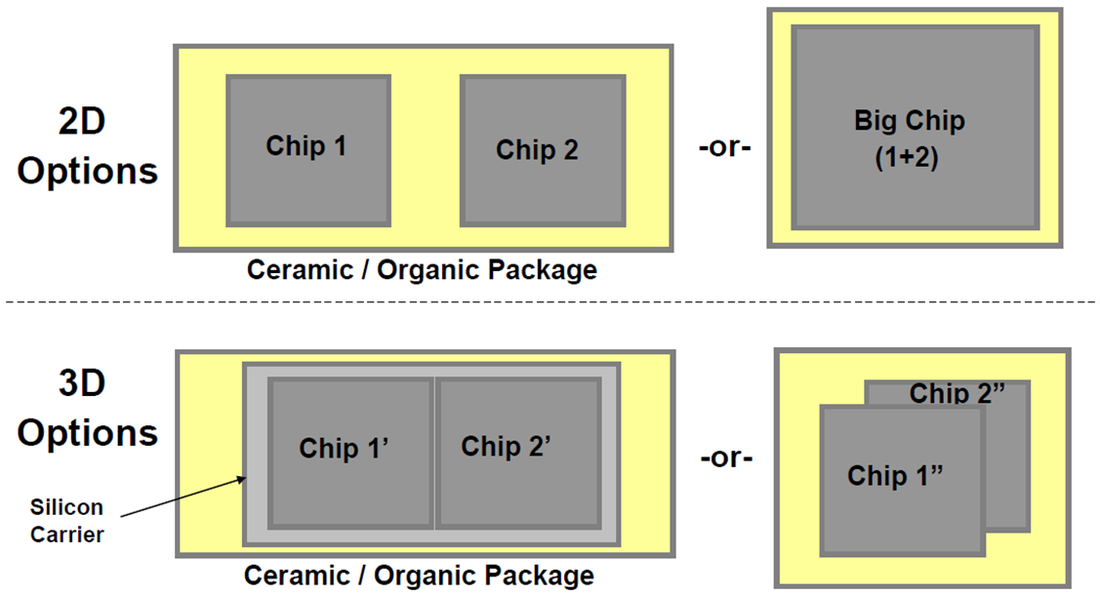

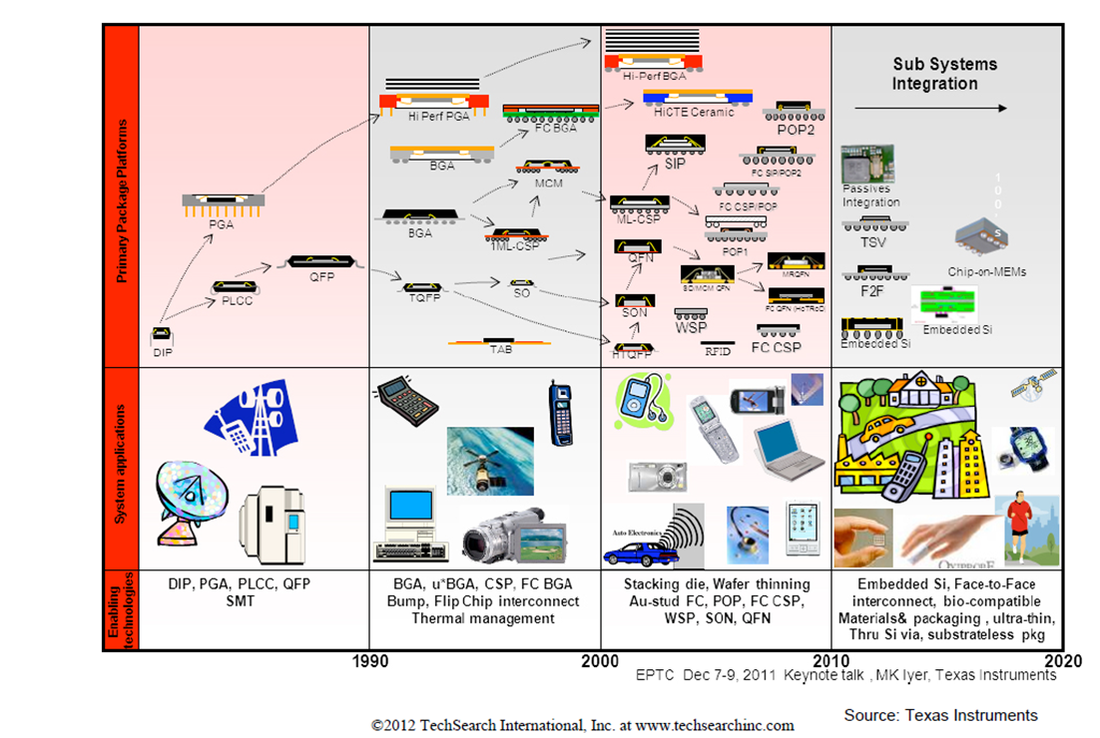

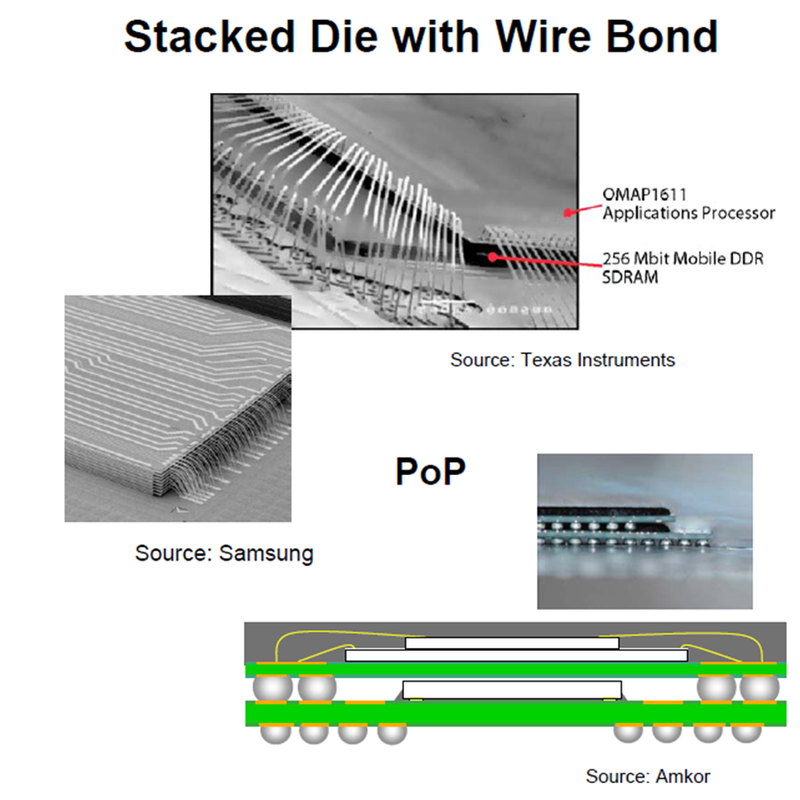

As well, utilizing 3D devices with TSV has, in the grand scheme, a similar outcome; namely, advancing the integration via 3D structures rather than continued scaling. Though in the future, 3D devices and advanced nodes could go hand in hand.

2. The big miss of the road map. When one looks at some old road maps from a few years ago, one can ask how did we, the industry, miss by so much?

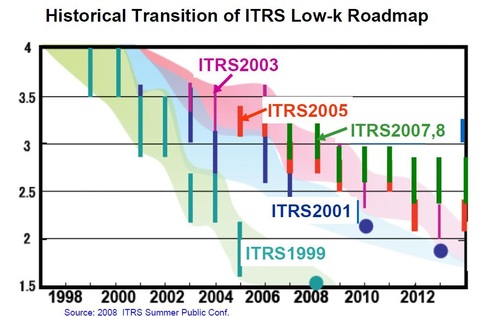

This actually reminds me of another miss from a few years ago-the low k inter-metal dielectric. Fig. 1 shows the low k dielectric roadmap trend of various ITRS published roadmaps and the prediction in 1999 that by 2004 we would be using k<2 !! Obviously we know what happened and even today 14 years later it is hard to breakthrough a k value of 2.5.

EUV: The EUV technology has so far gone through monumental achievements vis-Ã -vis the incredible tasks of developing the next generation stepper technology. The amount of engineering and resources poured into it is unprecedented in the short history of the semiconductor industry and maybe so for other industries.

It looks like as I write this blog that the only barrier for the technology from becoming a HVM tool is EUV source power that can provide a high enough throughput. Many experts doubt that it could ever be achieved; however, there are many other experts saying that it is within a reach.

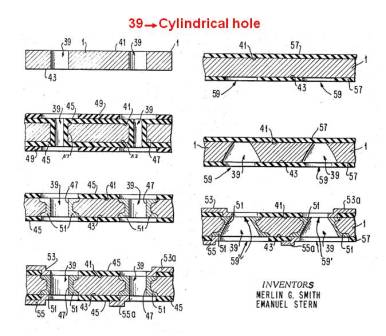

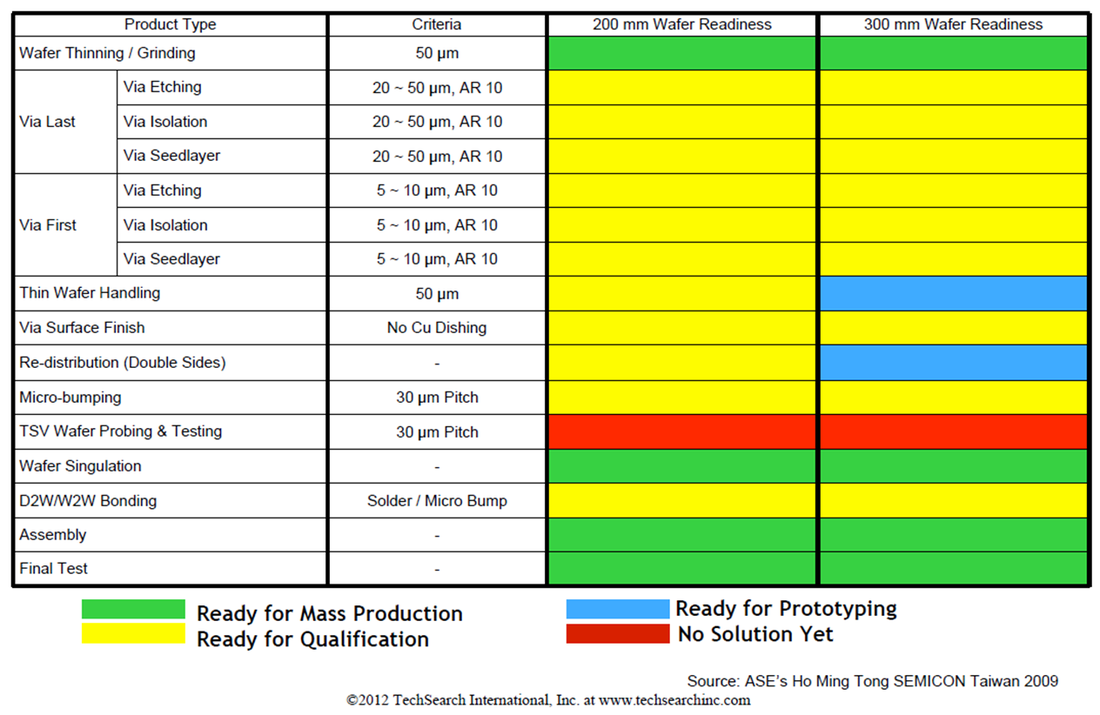

TSV: In this case I could see two totally unrelated issues:

1. Technology driven obstacles

2. Logistics and supply chain issues.

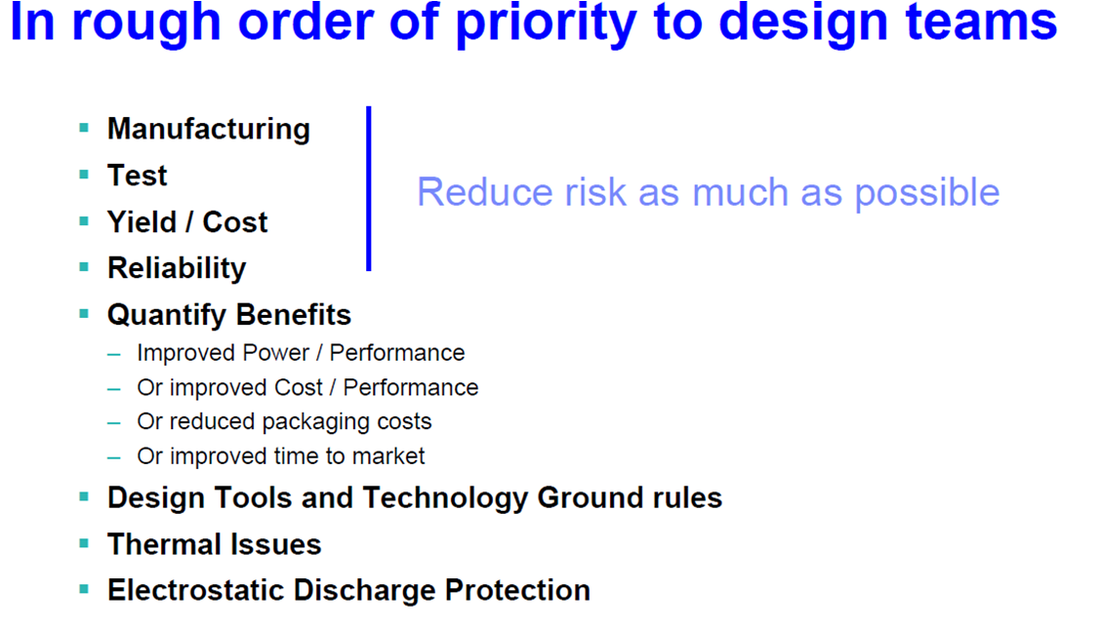

In the case of the TSV it is one of the few cases where the "power point" presentation(s) of the TSV idea are so convincing that it is actually hard to oppose it. However, when it comes to the fine details of the technology development, there are many issues that still need to be addressed and resolved. I believe that it is just a matter of time before the technical obstacles will be resolved and a unified standardized solution emerges. However, on the other hand, I see a real problem from the point of view of logistics, cost and supply chain of the technology, and I have some doubts if it can ever be resolved. For further discussion on this issue, please refer to: 3D IC Supply Chain: Still Under Construction, and to a detailed comment in EE Time published blog and comments re. Semicon West 3D - IC TSV, provided here below.

In summary, I believe that the industry will come with a solution for EUV before TSV becomes a production technology.

Yet there is another alternative to TSV and to EUV - it is the Monolithic 3D methods. Moreover, it is very likely that monolithic 3D will reach volume production before EUV and TSV. As we already see the NAND Flash vendors ramping up for production of 3D NAND.

The detailed comment fromm EE Times re. Semicon West 3D - IC TSV:

RSS Feed

RSS Feed