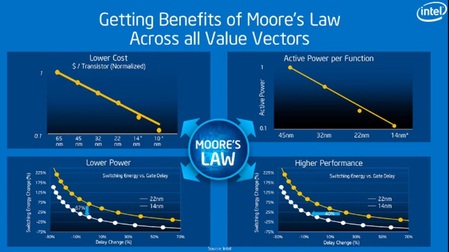

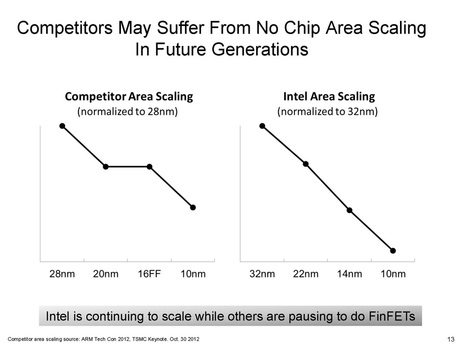

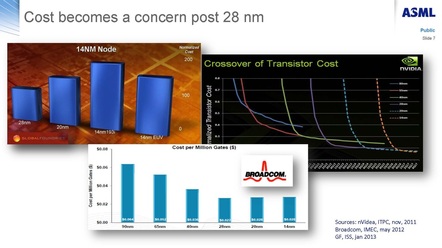

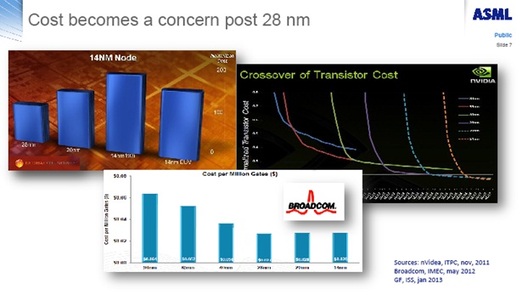

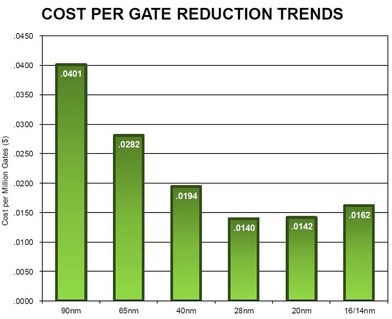

Intel clearly believes that it can beat the pure play foundries by an ongoing reduction of transistor cost while improving performance and power with dimensional scaling – essentially maintaining the trend of Moore's law just as in the past. Intel will “not take our foot off the pedal” of process technology, Krzanich explained, and he expects the company to be making parts as small as 10 nanometers in transistor size by 2015, versus today’s 22 nanometer parts. He was followed by Bill Holt, Intel’s EVP and head of semiconductor manufacturing, showing the following slide describing Intel expectations to drive down the cost per transistor.

Some may argue that Intel will have hard time competing due to the lack of broad EDA and IP support. This is also a valid point but Intel does not need to win all fabless designs. If Intel wins just the few super high volume designs, it may well win the war.

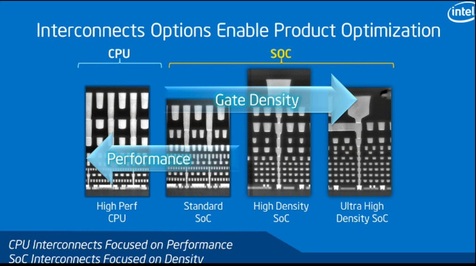

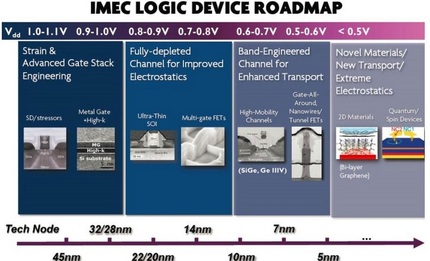

Some may argue that “Intel announced their high volume mobile SoFIA chips are mask fabricated at external foundry and do not use Intel internal manufacturing for at least next 2 years (2014-15). ALL of Intel's production for standalone modem chips today is outside Intel. Conclusion being Intel still does not have the right silicon technology for mobile computing which is why X86 less than 0.1% of Smartphone market" as one commenter at Intel Nears Foundry Inflection Point blog. This might be why Holt presented Intel’s plan to develop Foundry type processes. “Those products were optimized primarily for performance, and so Intel had avoided the problem that can crop up when transistors are packed more densely, namely that performance of the wires connecting transistors, the interconnects, can degrade. We didn’t scale the wires as much as we could have, because the products we were building didn’t demand that.” Now, he said, "the company’s technology would be focused more on those interconnects as Intel takes the scaling lead. The result would be the ability to more nimbly move between transistors optimized for performance, on the one hand, as in server and desktop chips, and transistors optimized for low-power mobile devices." as illustrated below:

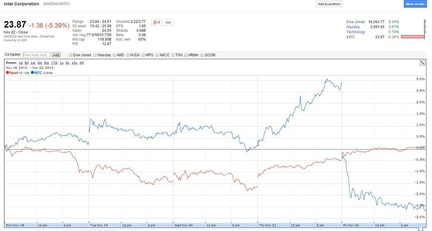

As TSMC's P/E is 14.42 while Intel's P/E is only 12.87 the market should have responded very well to these presentations but apparently it did not — and in reverse to NASDAQ trend, Intel stock fell more than 5% the day after:

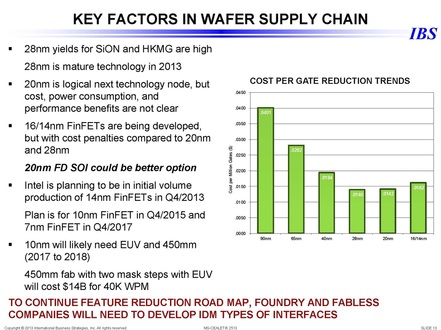

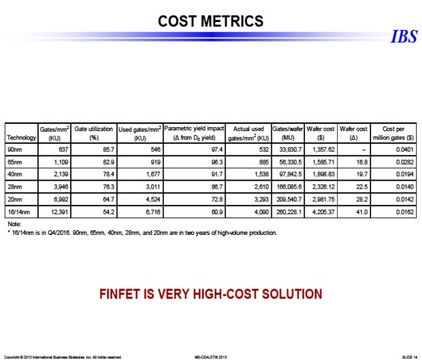

- Why did Intel feel the need to put so much money in the ASML EUV program if they can do just as well without EUV?

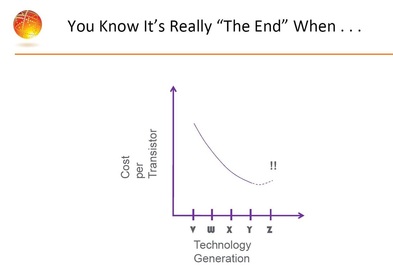

- Does Intel reduced cost per transistor account for its escalating cost of R&D, which in 2013 averaged more than 20% of revenue vs. less than 14% in 2005?

- Does Intel reduced cost per transistor account for its escalating cost of capital, which, per their balance sheet on Depreciation/Depletion, averaged in 2013 more than 26% of revenue vs. less than 10% in 2011?

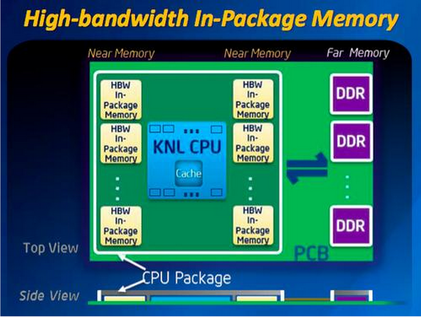

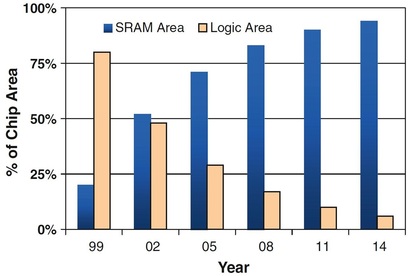

There is one more important issue that seems to be ignored. For SoC applications the embedded SRAM is a key factor because it dominates the die area, as we recently presented in our blog Are we using Moore’s name in vain?. If Intel’s embedded SRAM is scaling each node as before then it would represent an important advantage over the foundries. Yet Intel recently announced integration of DRAM into Haswell and promised future Xeon and Xeon Phi models that integrate memory atop processors in 3D packages instead. Will these be aggressive enough to keep the on-system memory costs scaling?

RSS Feed

RSS Feed