We start with the EE Times article IEDM goes deep on 3-D circuits, starting with "Continuing on the theme of 3-D circuit technology addressed in an earlier post about this year’s International Electron Device Meeting, Rambus, Stanford University and an interesting company called Monolithic 3D will address issues related to cooling 3-D circuits. .." and follow with a quote from the abstract to IEDMs short course "Emerging Technologies for post 14nm CMOS" organized by Wilfried Haensch, of IBM’s Watson Research Center:

"Scaling the dimension was the key for the unprecedented success of the development of IC circuits for the last several decades. It now becomes apparent that scaling will become increasingly difficult due to fundamental physical limits that we are approaching with respect to power and performance trade-offs. This short course will give an overview of several aspects in this “end-of-scaling” scenario. ..."

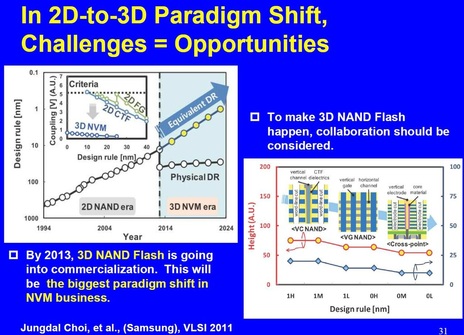

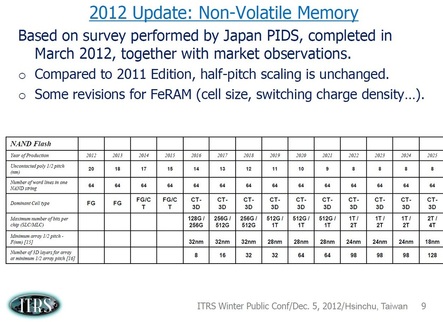

"Yet there are a variety of developments in another type of 3-D scaling that are likely to have a similarly large impact on semiconductors in the near future - 3-D devices for NAND flash.... And as in planar CMOS logic, NAND flash technology has been progressively scaled to smaller feature sizes, becoming the process leader in driving the smallest line-widths in manufacturing as evidenced by the current 1x-nm (~19-nm) process node. Yet, despite plans to scale down to the 1y-nm (~15-nm) and possibly 1z-nm (~13-nm) nodes, the traditional planar floating gate NAND flash architecture is approaching the scaling limit, prompting the search for new device architectures. Not to be upstaged by the planar to 3-D (FinFET) transition in logic devices, NAND flash has embarked on its own 3-D scaling program, whereby the stacking of bit cells allows continuous cost-per-bit scaling while relaxing the lateral feature size scaling."

The Current 2D-IC is Facing Escalating Challenges:

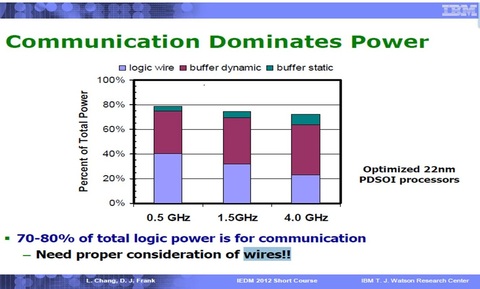

- On-chip interconnect (#1)

- Dominates device power consumption

- Dominates device performance

- Penalizes device size and cost

- Lithography (#2)

- Dominates Fab cost

- Dominates device cost and diminishes scaling benefits

- Dominates device yield

- Dominates IC development costs

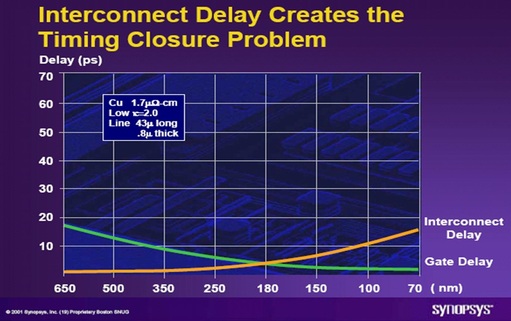

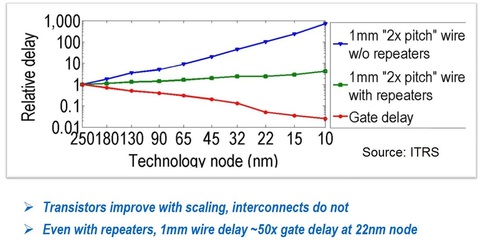

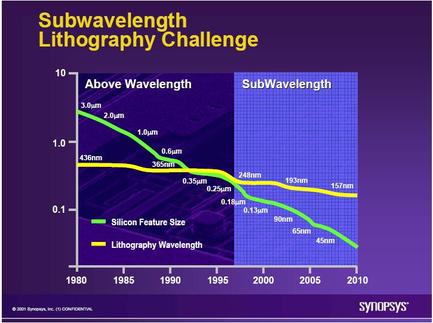

The problem with on-chip interconnect didn’t start today. This vintage Synopsys slide below clearly indicates that on-chip interconnect started to dominate overall device performance a decade ago:

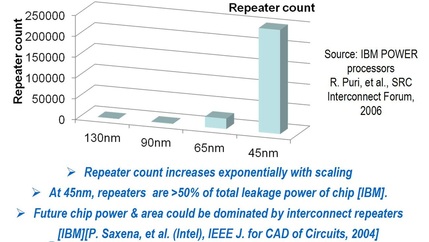

The practiced ‘band-aid’ fix so far has been throwing more transistors (they are getting cheaper, right? No longer. See father below) at the problem in the form of buffer and repeaters. But as we scale down we need exponentially more of these ban-aids as illustrated by the following:

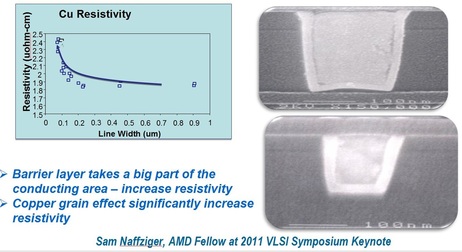

"The 14 nanometer node is expected to be an inflection point for the chip industry, beyond which the resistivity of copper interconnects will increase exponentially and may become a limiting factor in chip design. On December 11, 2012, Applied Materials, Inc. will host an important forum in San Francisco to explore the path that interconnect technology must take to keep pace with transistor scaling and the transition to new 3D architectures.” (emphasis added)

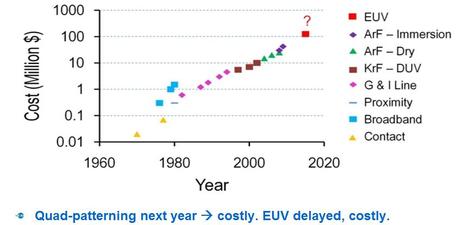

The following chart illustrate the lithography escalating cost of equipment which directly reflect the wafer cost.

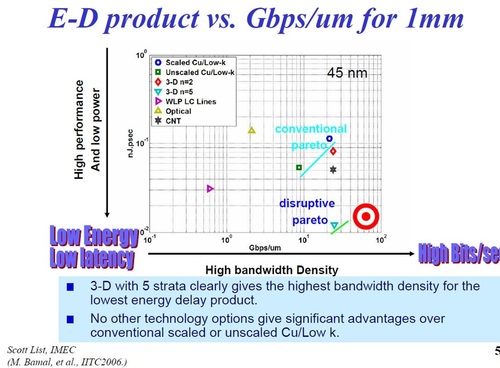

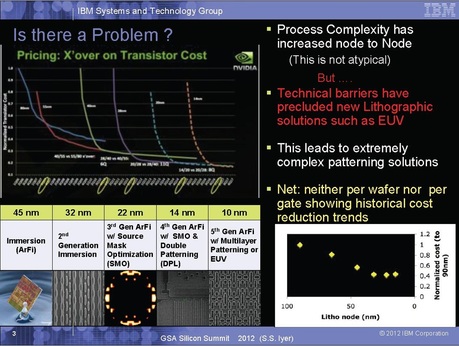

Another EE Times IEDM12 article covering a keynote given by Luc van den Hove, chief executive of IMEC, IEDM: Moore’s Law seen hitting big bump at 14 nm, repeats the same conclusion. In fact, some vendors are already changing course accordingly. GlobalFoundries, in its recent 14nm announcement, disclosed that the back-end will be unchanged from 20nm. This suggests a similar die size and respective increase in per-transistor cost. Further, ST Micro in the Fully Depleted Transistors Technology Symposium (11 December, 2012) during IEDM12 week also acknowledged that their 14nm node will have a 20nm node metal pitch, and, just like GlobalFoundries, a similar die size and increase in per-transistor cost. So it would seem that also for lithographic reasons, the industry’s next generation path, and the continuation of Moore's Law, would be achieved by leveraging the third dimension.

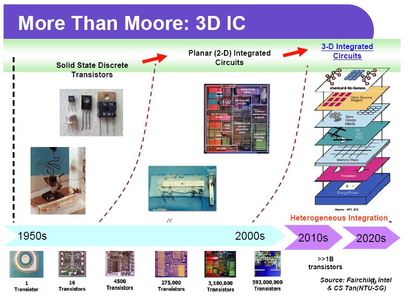

Now that monolithic 3D is feasible and practical, the time has come to move in this new direction, as has been nicely illustrated by this concluding chart below

RSS Feed

RSS Feed