Qualcomm has done more than just talking. It has been investing in monolithic 3D development tools with institutions such as Georgia Tech (see their GTCAD LAB website reporting technology transfer in 2012 and 2014). Qualcomm has been filing patents in this area and recently announced an agreement to work with CEA-Leti - Qualcomm to Evaluate Leti’s Non-TSV 3D Process

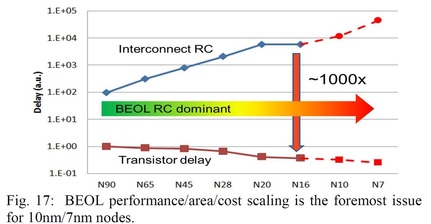

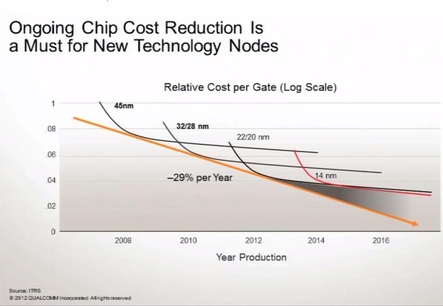

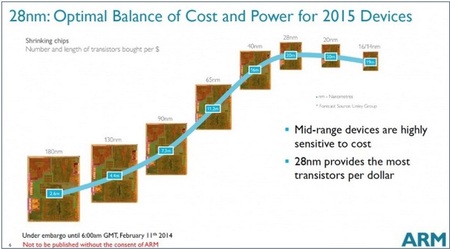

It would seem that the number one motivation behind these efforts is Qualcomm’s concern about future cost reductions. Early in 2012 Jim Clifford, Qualcomm's VP and GM (at that time), in his plenary talk at the SPIE conference titled - A Mobile Wireless Phenomenon: A Continued Need for Advanced Lithography, made it very clear with his second slide. At that time there were already some concerns with EUV’s rollout schedule. Jim called on the conference attendees to make sure to solve the escalation of advanced lithography cost, which was already dominating more than 50 % of the overall advanced device cost. Jim presented the following curve, showing the historical 29% cost reduction per year, and the looming problem with the production cost beyond 28 nm.

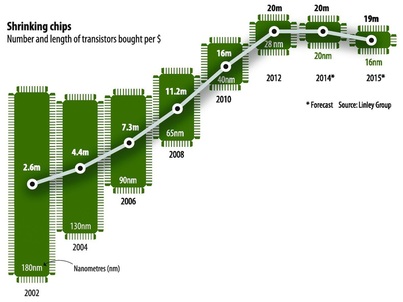

Back to the DAC 2014 keynote: Arabi explained: “Mobile is becoming a centre of gravity for the user. It is providing a unique opportunity ... but it becomes a challenge to develop because you have to integrate them at lower power and low cost as well ... One of the biggest problems is cost. We are very cost sensitive. Moore’s Law has been great. Now, although we are still scaling down, it’s not cost-economic anymore. It’s creating a big problem for us.” As we reported in our recent blog, 28nm – The Last Node of Moore's Law, dimensional scaling below 28 nm will result in increasing device cost. This was echoed multiple times at this DAC by other keynote speakers such as Hossein Yassaie, CEO of Imagination Technologies, who said: “Moore’s Law is really over from my point of view. It’s not that it can’t scale, it’s that the cost is not going down anymore".

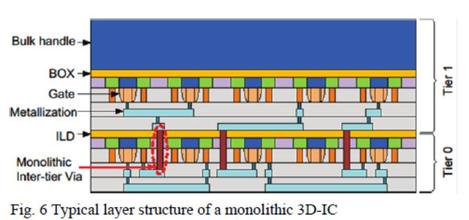

Clearly, monolithic 3D integration has a very important role for the future of the semiconductor industry. It is therefore fitting that the traditional IEEE conference on SOI has extended its scope and now calls itself S3S: SOI technology, 3D Integration, and Subthreshold Microelectronics. The 2014 S3S conference is scheduled for October 6-9, 2014 at the Westin San Francisco Airport. This would be a great opportunity to learn more about monolithic 3D technology with 5 invited presentations covering topics from design tools to monolithic 3D NAND and other 3D memories, CEA Leti will present their work on CMOS monolithic 3D IC, and researchers from MIT and Stanford will present manufacturing monolithic 3D devices with materials other than silicon.

RSS Feed

RSS Feed