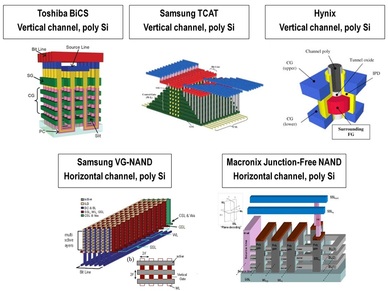

The key points to note are:

- Lithography steps for patterning multiple memory layers are shared, which lowers cost.

- Polysilicon is used as the channel material for transistors.

- To be cost-competitive with scaled 2D NAND flash memory, aspect ratios to be etched and filled are often 50:1 or higher. For future generations, aspect ratios need to be increased further!

The questions to ask are therefore: Can we build 3D NAND flash memories with single crystal silicon instead of polysilicon? In addition, can we use low aspect ratios and still have cost-competitive products? I will now describe MonolithIC 3D Inc.’s technology, where both these important problems are solved. We were awarded fundamental patent coverage on this technology just a few months back.

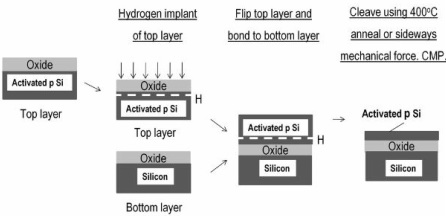

Ion-Cut: The Building Block

Process Flow

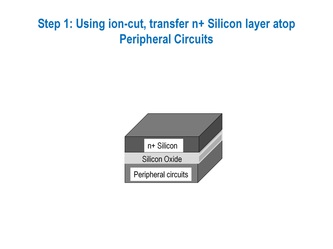

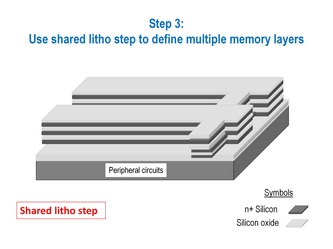

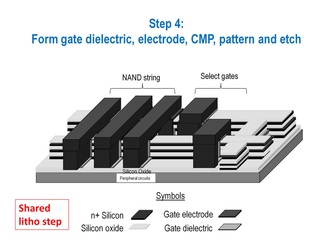

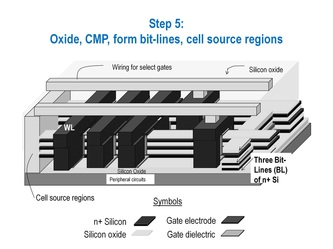

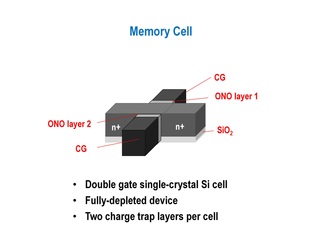

Figure 3 describes the process flow for constructing our company's monolithic 3D NAND flash memory technology. The key point to note is how lithography steps for patterning multiple memory layers are shared, keeping cost per bit down. The memory cell is a double gate depletion mode single crystal silicon transistor that utilizes charge-trapping as the storage mechanism.

(Click on any of the above images to enlarge)

The steps involved in this process are:

- Step 1: Ion-cut is used to transfer a n+ single crystal silicon layer atop the peripheral circuits as depicted in Figure 3. Notice how the peripheral circuits are placed under the memory array... this improves array efficiency. Tungsten may be used for the wiring of the periphery.

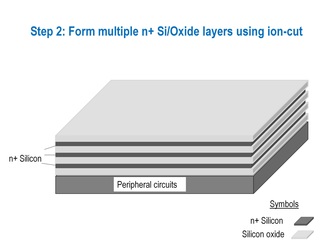

- Step 2: Using steps similar to Step 1, a silicon-silicon dioxide multilayer sandwich is formed as described in Figure 3. A high temperature anneal may be conducted (if desired) to reduce defect levels in the layer transferred silicon.

- Step 3: Using the same litho and etch step, multiple layers of memory are defined.

- Step 4: Gate dielectrics and electrodes are formed for multiple levels of memory at the same time.

- Step 5: Cell source regions are formed. Contacts to multiple levels of memory are defined with shared litho steps using a process described in [Tanaka, et al., Symposium on VLSI Technology, 2007]. Figure 3 reveals the structure after this step. Using carefully chosen biases to bit-lines (BLs), word-lines (WLs) and the cell source, bits in the memory array can be accessed.

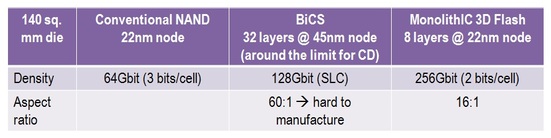

Figure 4 gives estimates for density and aspect ratio based on data presented at the 2010 VLSI Symposium Short Course. MonolithIC 3D Inc.'s single crystal silicon solution can provide 4x higher density than conventional NAND flash memory at the 22nm node. Aspect ratios are manufacturable, unlike today's poly-based solutions.

Our technology is, of course, applicable to any monolithic 3D NAND flash memory architecture where the transistor's channel is horizontal. For more details, please check out our issued US patent #8,026,521 or contact me by e-mailing [email protected].

- Post by Deepak Sekar

RSS Feed

RSS Feed