Karim Arabi, Qualcomm VP of Engineering, voiced the strongest support and provided many details of monolithic 3D’s role, in his keynote at this year’s DAC. A good summary was posted at the Tech Design Forums site under the title "3D and EDA need to make up for Moore’s Law, says Qualcomm". In this blog I’ll highlight some of the very interesting quotes from Arabi’s keynote: "Qualcomm is looking to monolithic 3D and smart circuit architectures to make up for the loss of traditional 2D process scaling as wafer costs for advanced nodes continue to increase...One of the biggest problems is cost. We are very cost sensitive. Moore’s Law has been great. Now, although we are still scaling down, it’s not cost-economic anymore"

Karim Arabi, Qualcomm VP of Engineering, voiced the strongest support and provided many details of monolithic 3D’s role, in his keynote at this year’s DAC. A good summary was posted at the Tech Design Forums site under the title "3D and EDA need to make up for Moore’s Law, says Qualcomm". In this blog I’ll highlight some of the very interesting quotes from Arabi’s keynote: "Qualcomm is looking to monolithic 3D and smart circuit architectures to make up for the loss of traditional 2D process scaling as wafer costs for advanced nodes continue to increase...One of the biggest problems is cost. We are very cost sensitive. Moore’s Law has been great. Now, although we are still scaling down, it’s not cost-economic anymore"

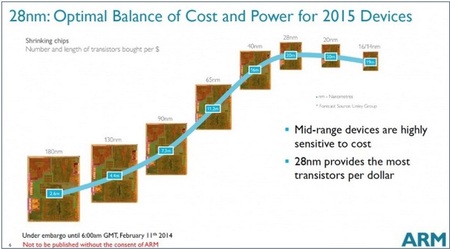

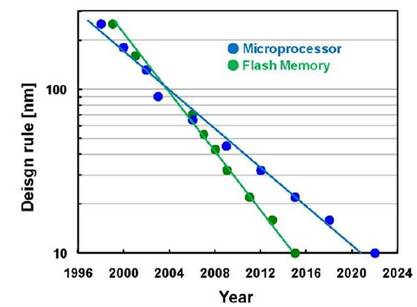

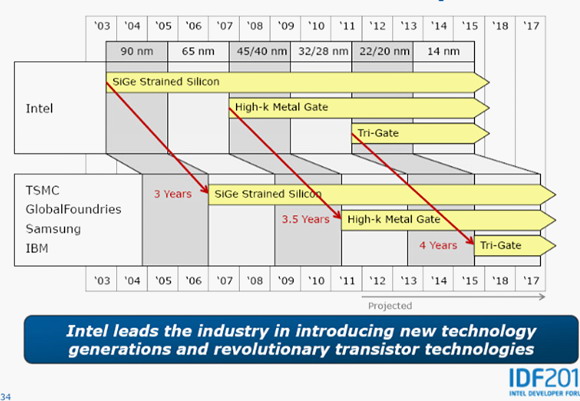

Qualcomm is not the only fabless company voicing its concern with cost. Early in 2013 Nvidia said it is "deeply unhappy" and executives of Broadcom followed suite. The following chart, presented by ARM, illustrates it nicely.

Yet eSRAM scales far less than 2X and, accordingly, for most SOCs, scaling would be even more costly. This issue has been confirmed again with the recent VLSI 2014 paper "10-nm Platform Technology Featuring FinFET on Bulk and SOI" by Samsung, IBM, STMicroelectronics, GLOBALFOUNDRIES and UMC. They presented that the size of their 10 nm bitcell is 0.053 µm², which is only 25% smaller than the 0.07 µm² reported for 14 nm bitcell size. One should expect that an additional area penalty would occur for effective use in large memory blocks, as reported even for 14nm, which could bring the effective SRAM scaling to only about 15%, a long way from the 50% required to neutralize the escalating wafer costs.

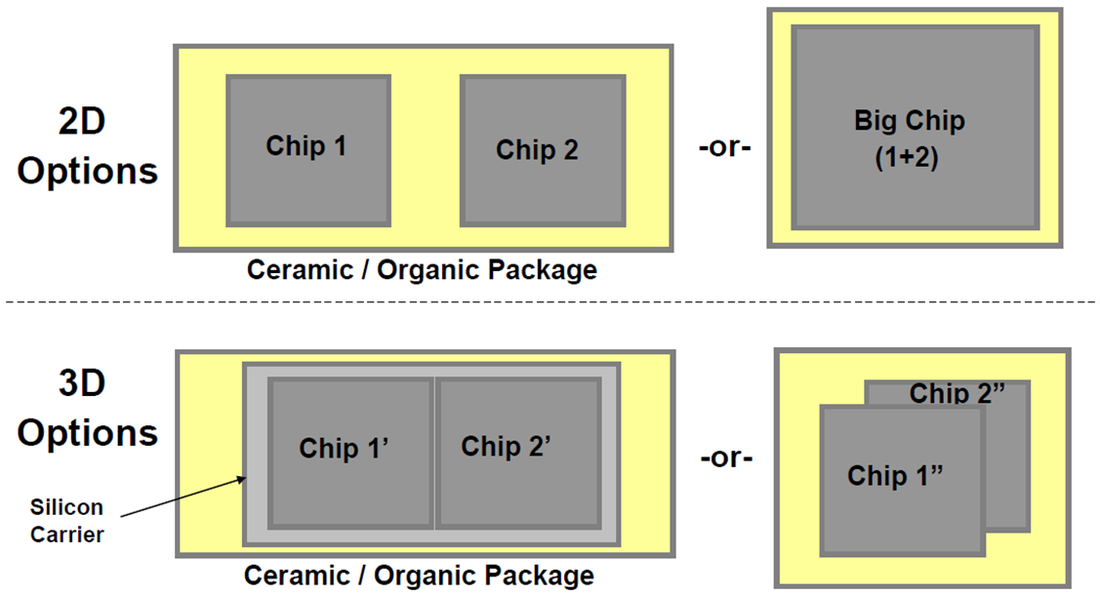

However, cost is not the only issue that forced Qualcomm to consider monolithic 3D. Quoting Arabi:

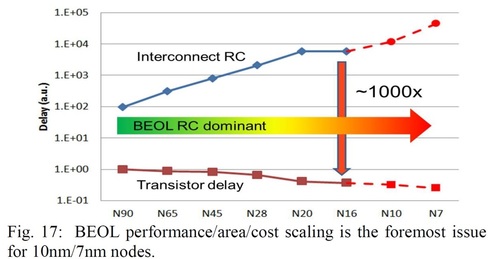

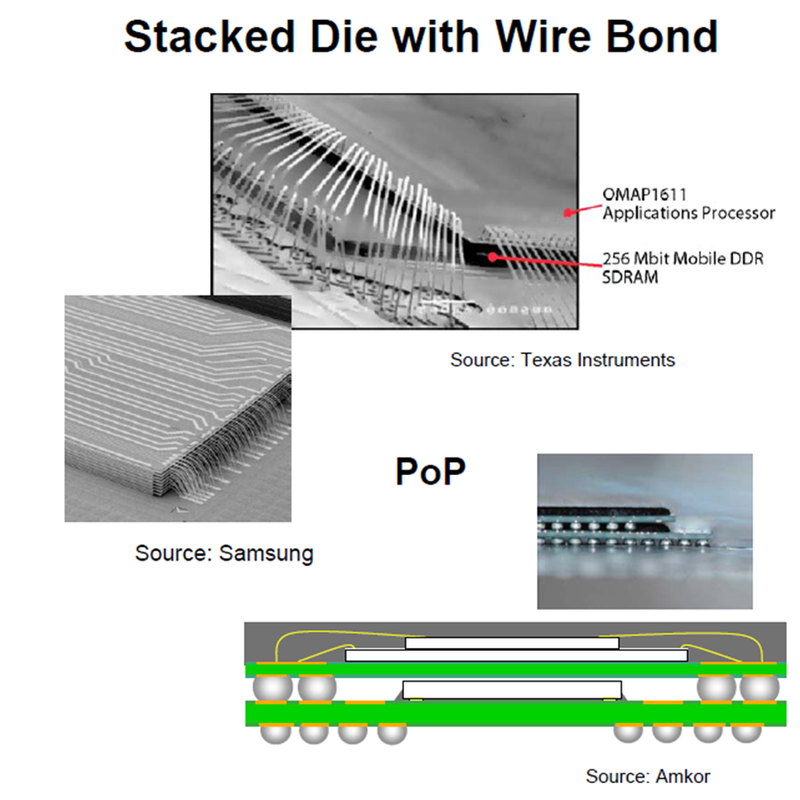

“Interconnect RC is inching up as we go to deeper technology. That is a major problem because designs are becoming interconnect-dominated. Something has to be done about interconnect. What needs to be done is monolithic three-dimensional ICs. Through-silicon vias and micro bumps are useful where you need I/Os ... But they are not really solving the interconnect issue I’m talking about ... So we are looking at true monolithic 3D. You have normal vias between different stacks. Then interconnect lengths will be smaller than with 2D. If we can connect between layers the delay becomes smaller."

The interconnect issue was also addressed at IEDM 2013 by Geoffrey Yeap, Qualcomm VP of Technology, in his invited talk:

"As performance mismatch between transistors and interconnects continue to increase, designs have become interconnect-limited. Monolithic 3D (M3D) is an emerging integration technology poised to reduce the gap significantly between transistors and interconnect delays to extend the semiconductor roadmap way beyond the 2D scaling trajectory predicted by Moore’s Law."

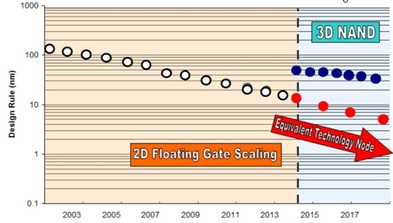

Yeap provided the following chart for the growing gap between transistor delay and interconnect delay:

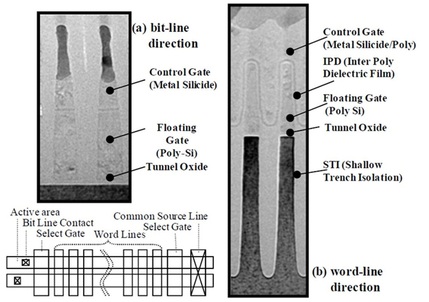

Clearly, monolithic 3D integration has a very important role in the future of the semiconductor industry. It is therefore fitting that the traditional IEEE conference on SOI has extended its scope and now calls itself S3S: SOI technology, 3D Integration, and Subthreshold Microelectronics. The 2014 S3S conference is scheduled for October 6-9, 2014 at the Westin San Francisco Airport. This would be a great opportunity to learn more about monolithic 3D technology, with 5 invited presentations covering topics from design tools to monolithic 3D NAND and other 3D memories. CEA Leti will present their work on CMOS monolithic 3D IC, and researchers from MIT and Stanford will present manufacturing monolithic 3D devices with materials other than silicon.

RSS Feed

RSS Feed