Masuoka came back to the IEDM in 1987 and suggested a Flash NAND structure [2].

Intel created the first commercial NOR type of Flash chips in 1988. For the next few years some major developments occur in the Flash arena:

- In 1989, Samsung and Toshiba created a NAND flash memory.

- In 1994, Compact Flash was invented and introduced by SanDisk.

- In 1999, the SD memory card was released by a combination of SanDisk, Toshiba and Matsushita.

- In 2001, the world’s first 1 Gigabit Compact Flash card was introduced.

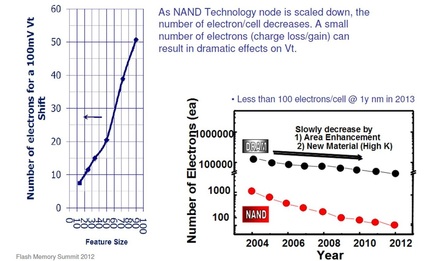

Physical Limitations:

- Pattern scaling - lack of EUV is a major issue

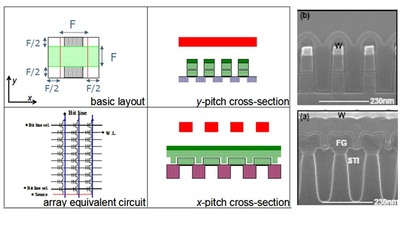

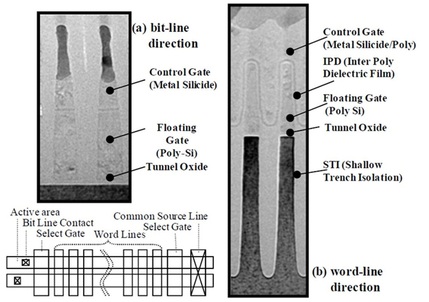

- Structure formation, Figure 4 depicts a 27nm NAND cell that shows how close the cells are getting to each other, and how much the aspect ratio is getting out of hand. This is a limiter to obtaining high yield.

- There is an increase in cell-to-cell interference in the word lines.

- Capacitive coupling ratio has decreased

- Dielectric leakage has increased

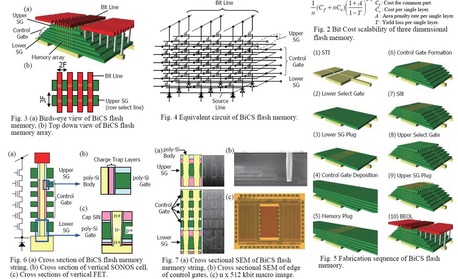

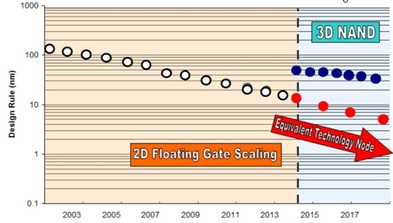

The solution for this dilemma is the 3D NAND, which was initially proposed by Toshiba at the 2007 VLSI Symposium [3]. Toshiba unveiled its Bit Cost Scalable (BiCS) technology. BiCS makes use of a “punch-and plug†structure and charge trap memory films. Toshiba has fabricated a prototype 32-Gbit BiCS flash memory test array with a 16-layer memory cell using 60nm design rules, see Figure 6. Hynix, Samsung and Macronix have also come with their versions of the 3D NAND.

- With 3D NAND, scaling is no longer driven by lithography. The gate length is defined by deposition

- The key steps to 3D NAND are

- Fill the deep memory holes or trench slits. The top foreseeable challenges are ultra-high-aspect ratio (>40:1) conductor etch and dielectric etch with high etch selectivity to the hard mask

- 3D NAND is relatively straightforward for a DRAM maker since it has stacked SiO2 and polysilicon layers like a stacked capacitor DRAM, and trenches like a trench cell DRAM.

- 3D NAND is evolutionary, not revolutionary.

- The good news is continued cost reduction, smaller die sizes and more capacity.

- Installed NAND toolsets in the wafer Fabs can, for the most part, be reused, thereby extending the useful life of Fab equipment.

- 3D NAND technology is still basically NAND with all its inherent limitations of data reliability and performance: hence, generally well understood (evolutionary).

It is not too difficult to see the similarity between the up and coming 3D NAND and the Monolithic 3D approach. As we describe in our web site (www.monolithic3d.com) the advanced technology patented by MonolithIC 3D Inc. enables the fabrication of Monolithic 3D Integrated Circuits with multiple stacked transistor layers and ultra-dense vertical connectivity. Thus, it appears monolithic 3D-ICs with 2 device layers provide benefits similar to a generation of conventional scaling. Furthermore, just as conventional scaling reduces feature sizes every generation, monolithic 3D opens the road for many years of continuous scaling by ‘folding’ once, twice, and so forth without necessarily reducing feature sizes.

- F. Masuoka et. al IEDM 1984 pp464-467

- F. Masuoka et. al IEDM 1987 pp552-555

- H. Tanaka et al., Symp. on VLSI Tech. Dig., pp 14-15, 2007

RSS Feed

RSS Feed