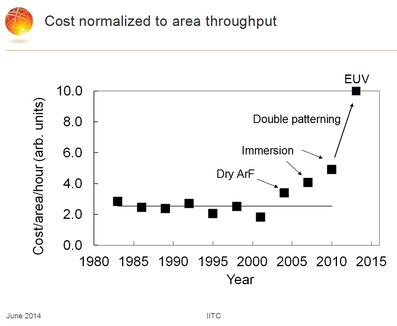

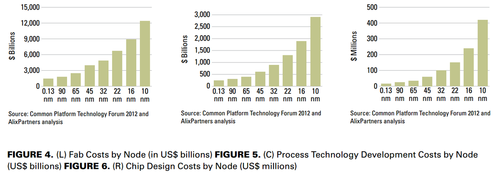

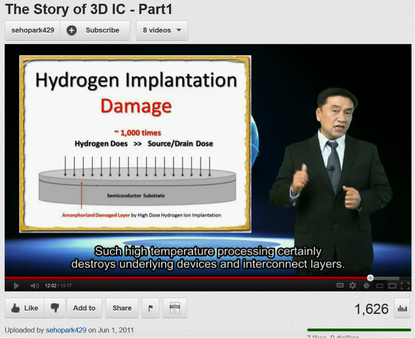

Recent blogs such as Established Nodes Getting New Attention and Moore's Lag Shifts Paradigm of Semi Industry have articulated the building up of interest in SOI, Sub-threshold and 3D IC technologies. The IEEE S3S is the conference to learn and get updated on these technologies and M3DI is that newest part integrated into the conference. The 3D part of S3S 2014 will have a full day of tutorial presentations by leading researchers in the space, a full session of invited papers, and will conclude with a session dedicated to discussing the most recent breakthroughs in the field.

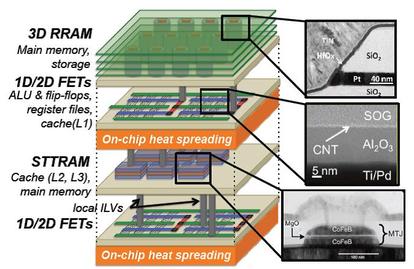

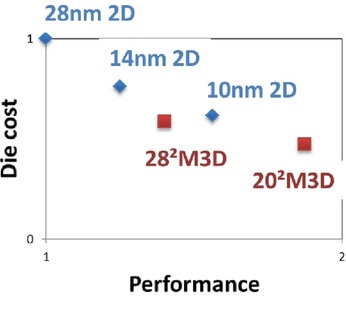

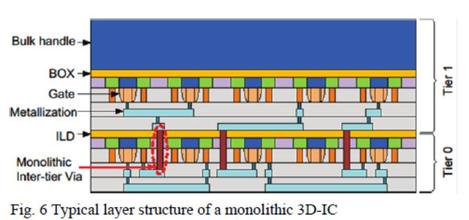

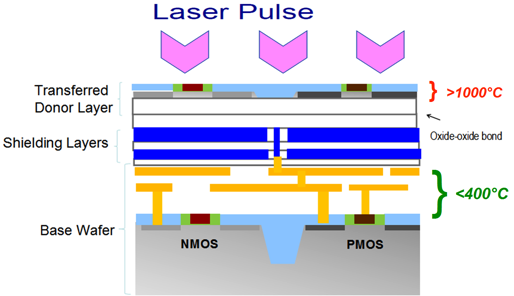

The M3DI short course will cover alternative process flows that enable M3DI, discuss the challenges and solutions to removal of the operating heat of monolithic 3D stacks, and describe the range of powerful advantages provided by M3DI. Subsequently, Prof. Sung Kyu Lim of Georgia Tech will cover EDA for M3DI. This will be followed by broad coverage of M3DI for memory applications by two leading experts in the field, Akihiro Nitayama of Toshiba/Tokohu University and Deepak Sekar of Rambus. M3DI provides unparalleled heterogeneous integration options which will be covered by Prof. Eugene Fitzgerald of MIT and SMART Lee Institute of Singapore describing the integration of silicon with other crystals for electro-optic device integration. The short course will conclude with Prof. Philip Wong of Stanford, who leads research efforts to integrate silicon with carbon nanotube and advanced 2D transistors layered with memory such as STT-MRAM and RRAM.

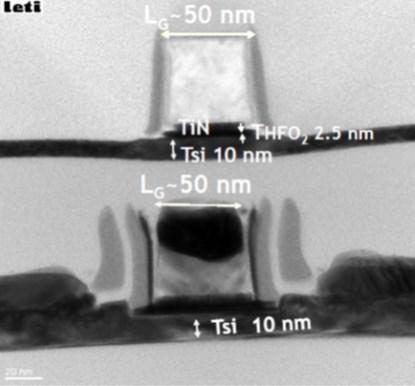

For a postprandial enjoyment, CEA Leti will present in the Late News session a fully constructed M3DI SOI device, and IBM will present its Multi Stacked Memory Wafer technology.

More information is available on the conference site: S3S Conference 2014

RSS Feed

RSS Feed