|

We have a guest contribution from Zvi Or-Bach, the President and CEO of MonolithIC 3D Inc.

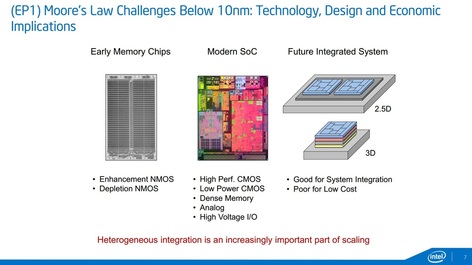

This year Semicon West had a clear undertone – the roadmap forward is 3D IC. Yes, we can and we will keep pushing dimensions down, which for a few applications would be attractive, but for most designs the path forward would be “More than Moore.” |

2015-LetiDay-SanFrancisco

- Welcome - Leti's 3D integration for tomorrow's devices > M.N Semeria

- CoolCubeTM: 3D sequential integration to maintain Moore's Law > O. Faynot

- Photonics: why 3D integration is mandatory > H. Metras

- Computing: 3D technology for better performance > S. Cheramy

- Lighting: 3D integration for cost effectiveness > I. C Robin

- Nanocharacterization for 3D > P. Bleuet

- Conclusion - Silicon Impulse > M.N Semeria

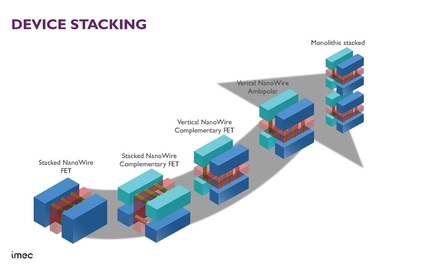

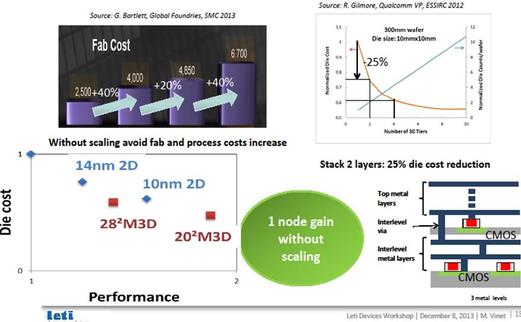

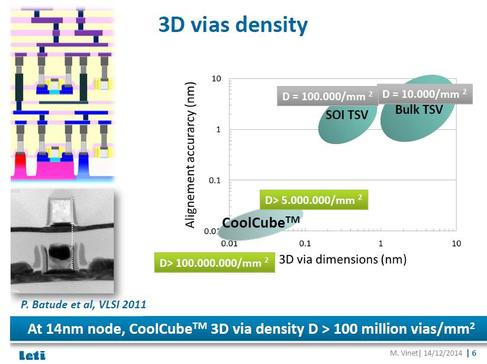

These limitations are the driver behind the efforts to develop monolithic 3D technology. Monolithic 3D would provide a very cost effective alternative to dimensional scaling with 10,000x higher than TSV vertical connectivity, as illustrated by the following two slides of CEA Leti.

While stacking using TSV does not require any change to the transistor (‘front-line’) process flow, all monolithic 3D process flows until recently required a significantly new transistor formation flow. Since the transistor process is where the majority of the R&D budget and talent is being allocated, and carries with it fresh reliability concerns, the industry has been most hesitant with respect to monolithic 3D adoption. Yet in this recent industry gathering there is a sense that industry wide interest is building up for 3D technologies. The success of 3D NAND as the first monolithic 3D industry wide adoption could help this new interest build even faster.

There is room for even more excitement. A recent technology breakthrough, first presented in IEEE S3S 2014 conference (Precision Bonders - A Game Changer for Monolithic 3D) introduced a game changer in the ease of monolithic 3D adoption. Enhancement of this breakthrough will be presented in this year’s IEEE S3S 2015. This new monolithic 3D flow allows the use of the existing fab transistor process for the fabrication of monolithic 3D devices, offering a most attractive path for the industry future scaling technology.

P.S.

A good conference to learn about these new scaling technologies is the IEEE S3S ‘15, in Sonoma, CA, on October 5th thru 8th, 2015. CEA Leti is scheduled to give an update on their CoolCube program, three leading researchers from Berkeley, Stanford and Taiwan’s NLA Lab will present their work on advanced monolithic 3D integration technologies, and many other authors will be talking about their work on monolithic 3DIC and its ecosystem.

RSS Feed

RSS Feed