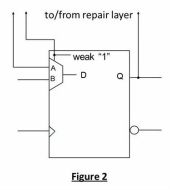

Today I will describe an alternative method that addresses the repair of multiple stacked layers of logic by a single stacked repair layer. Like before, this method offers close to 100% yield and enables super large scale integration devices up to a wafer size.

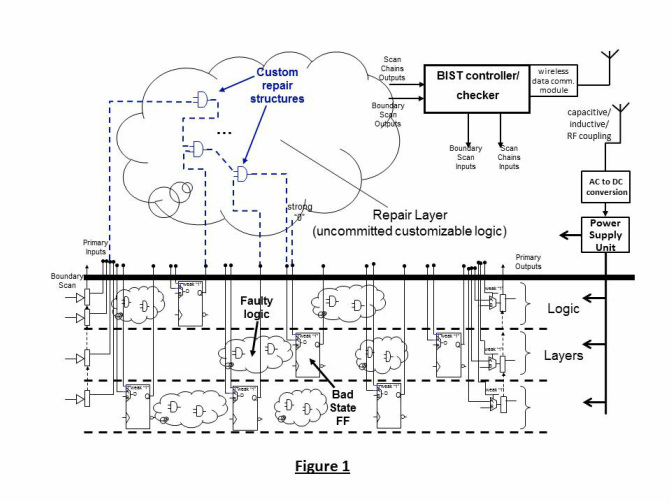

A few points are worth noting. First, since the vertical distance added by each layer is on the order of a micron, the distances (and timing) are essentially preserved when using the repair layer. Further, the transistors on the repair layer can be made somewhat faster (and more power hungry) than the logic layer transistors, as only a handful of the repair transistors will ever be actually used; hence their impact on the overall power dissipation is miniscule. Second, in a typical manufacturing flow one expects faults on the order of one per square centimeter or less and, even with multiple stacked layers, a single repair layer contains plenty of transistors available to effect repairs of a few logic cones at this fault density. Third, it should be noted that this particular approach does not address the case when the fault is in the flop itself. Flops typically occupy only a fraction of the silicon area and the impact of this restriction on yield is minimal.

One may wonder how realistic the contactless approach to testing wafers is. Just last month ST Microelectronics announced first commercial wafer-level contactless testing. At the 2011 ISSCC, Keio University (Yokohama, Japan) researchers announced inductive harvesting of 6 watts of energy with a 5x5 mm square chip. A year before that they demonstrated a 6 Gb/s wireless transfer rate per pin with a 300x300 micron antenna size, and in 2009 a group from the same university demonstrated contactless probing that can perform DC measurement. (The links require IEEE subscription). Clearly, contactless testing is coming just in time to assist with the testing of large 3D chips.

RSS Feed

RSS Feed