Threshold voltage variations are usually manageable in current digital circuits by sweeping them under the noise margin rug. However, as many of you very well know, shrinking of device dimensions leads to higher overall power consumption and necessitates lowering the supply voltage. Pretty soon, we will run out of rug space to sweep under!

As a review, let’s discuss the two big reasons why we need to scale down the supply voltage as we scale down device dimensions. The first and obvious reason is to ensure the physical integrity of the devices and avoid breakdowns. Smaller devices and thinner oxides simply can’t handle extreme electric fields.

The second reason has to do with power consumption, and there are a few aspects to this. Let us consider a single CMOS gate. For this case, if we ignore the short-circuit dissipation, the dynamic power PD is described by the familiar:

(1)

Static power PS can be summarized as:

(2)

There are however, also several reasons as to why we can’t keep scaling down the supply voltage. The first is that there are intrinsic material parameters that cannot be changed significantly, much less scaled, which include the bandgap energy and built-in junction potential of Silicon. Furthermore, the scaling potential of the MOSFET threshold voltage is very limited. For example, the sub-threshold leakage current for a device with a threshold voltage of 200mV is way too high and it will be hard to turn the device off. Lastly, the threshold voltage variations due to process fluctuations will force us to actually RAISE the threshold voltage to avoid having some small percentage of devices that don’t turn off.

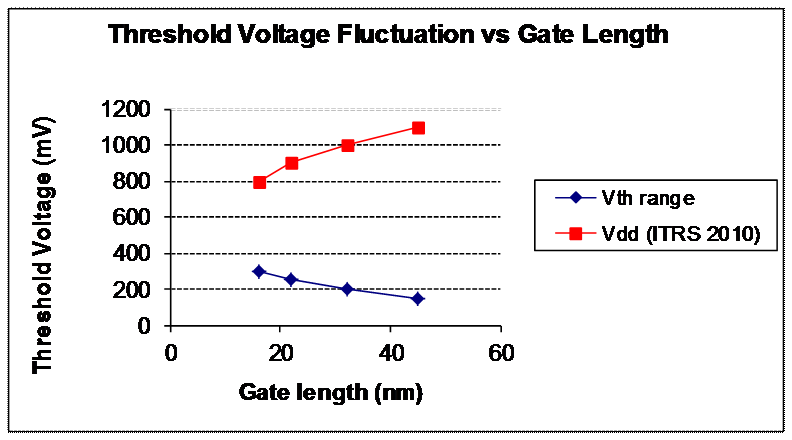

Let us look again at the chart (Figure 1) from my previous blog post showing the trends of the supply voltage and the range of threshold voltage variations versus gate length.

Figure 1 from Device Variability and Scaling

At the gate length node of 16nm, we can see that we need to raise the threshold voltage above 400mV just to accommodate the range of the threshold voltage variations, approaching the predicted 800mV supply voltage for that node. I can’t even imagine how difficult it would be beyond the 16nm node! At nodes further than 16nm, developing a manufacturing process that can handle the process variations AND maintain good yield will be prohibitively expensive. It seems that the only choices we have are either to switch to different materials (e.g. Germanium, III-V’s) or slow down scaling and go up (e.g. monolithic 3D).

RSS Feed

RSS Feed