A few weeks back, I received a paper titled "The Future of Microprocessors" from a colleague. Hmmm, I thought, that's a bold title to use. A quick look showed me the article was written by two well-known names in our industry: Shekhar Borkar, a Fellow at Intel and Andrew Chien, the VP of Intel Research (Chien left Intel recently to become a Professor at the University of Chicago). The paper was published in May 2011 in the Communications of the ACM. Let me first summarize the paper's contents... I will then share with you my thoughts on its message.

The Problem Statement

Microprocessor performance has improved by a factor of 30x every decade for the past 40 years. This 30x number should be our goal for the next decade, say Borkar and Chien. The main complication is meeting these goals in today's scenario where transistor scaling provides decreased benefits. When supply voltage reduces by 5%, clock frequency increases by 15% and capacitance decreases by 25% every generation, one can get just a 2.5x performance benefit in a decade for dual-core chips, say the authors. This is well short of the 30x required. Can we innovate and get around this issue?

Multiple Cores, Heterogeneous Cores

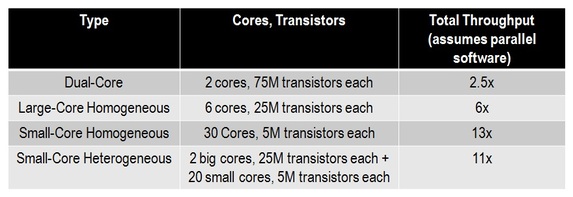

By moving to multiple small cores or a combination of many small and big cores, the maximum throughput increase we can get is greater than 10x, according to Borkar and Chien. Please see the table below. This brings us closer to our 30x goal, but the numbers assume software is completely parallel :-(

Extreme Circuits, Variability and Resilience

In a heterogeneous multi-core architecture, some cores could be operated at very low supply voltages close to the threshold voltage. This can provide an order of magnitude higher energy-efficiency. The loss of performance from low supply voltages can be compensated by operating multiple cores in parallel. However, significant issues with variability arise, since performance can fluctuate dramatically with threshold voltage variations. Various techniques to handle this issue could be used in future microprocessors, such as in-field diagnosis, reconfiguration and adaptability.

Handling Interconnect Issues

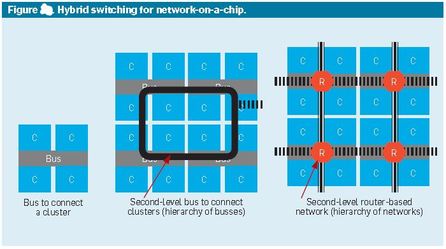

Borkar and Chien say that in a decade's time, as much as 90% of a chip's energy budget could be used to just communicate data to execution units from memory. To tackle this issue, they suggest that future microprocessors could have large register files close to execution units. While large register files are considered a no-no for performance reasons today, the authors say that in the future when raw frequency is not our key constraint, this could be ok.

Software

Borkar and Chien say that the move to heterogeneous multi-core architectures could bring up "the greatest software challenge in the history of computing". This is because the burden of extracting parallelism and enabling high performance is largely in the hands of the software developer.

Do I agree with the authors' vision of "the future of microprocessors"?

The paper is an interesting one. My main concern with this vision is that it puts much of the burden of getting performance in the hands of software developers, and gives them the hard task of programming for these complex chips. I've played a bit with parallel programming using APIs such as OpenMP. It's really hard! If Intel indeed goes this route, they will stand the risk of customers not seeing enough performance benefits due to the lack of parallelism in software. All this will translate to lower PC growth rates, which is bad for Intel's business.

I also feel microprocessor evolution will be more balanced, with process, device, circuit, architecture and software technologies all sharing the burden and improving performance. I was surprised not to find Finfets, 3D stacking of DRAM, monolithic 3D-ICs and other next-generation technologies covered in this vision for the "future of microprocessors". Borkar and Chien talk about post-silicon CMOS switches made out of carbon nanotubes, graphene and compound semiconductors, but don't discuss Finfets and 3D-IC approaches, which could be a lot more practical.

This being said, I liked the paper. It has many interesting circuit and architecture ideas. Shekhar Borkar plays a key leadership role within Intel's circuit research team, and the points he makes about next-generation circuits are very valid.

RSS Feed

RSS Feed