"Innovations for Next Generation Scaling"

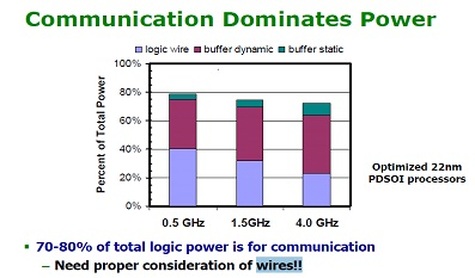

- On chip interconnect

- Lithography

- Logic Plane

- Memory Plane

- Photonic Plane

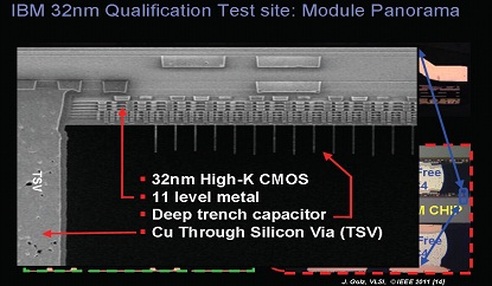

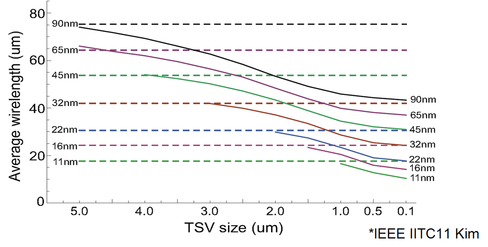

Now, here is my failure to understand. As a company who has been in the forefront of 3D and TSV research, IBM is well aware of the severe limitations of TSV as an alternative for vertical interconnect. The following cross-sectional picture by IBM, presented at the recent GSA Summit, clearly illustrates how large a TSV is in comparison to an interconnect via.

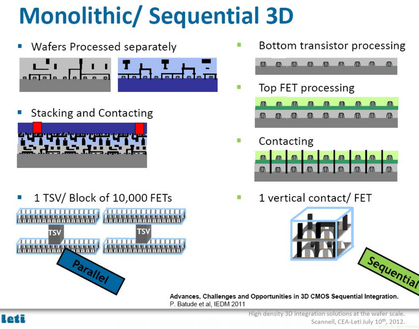

And particularly now, when monolithic 3D is finally practical, and the NAND Flash memory vendors are adopting it across the board!?

RSS Feed

RSS Feed