It is fitting to point to the comment made to EE Times coverage on Semicon West – 13 Things I Heard at Semicon West: “No matter what Intel says, Moore’s Law is slowing down,” said Bob Johnson, a semiconductor analyst for Gartner. “Only a few high-volume, high-performance apps can justify 20 nm and beyond.” He sees problems ahead for logic chips in general,” and to follow with quotes from another EE Times article – Silicon Highway Narrows, Twists: “Most foundries have yet to start buying the capital equipment needed for the 14/16 nm node, which for many will be the first to support FinFETs, says Trafas of KLA-Tencor. Gear companies hope the orders start coming in the fall…Indeed, he says, one of the big questions many capital equipment execs will bring to this year’s Semicon West event on July 7 is, “When will the 16/14 nm investments begin?”

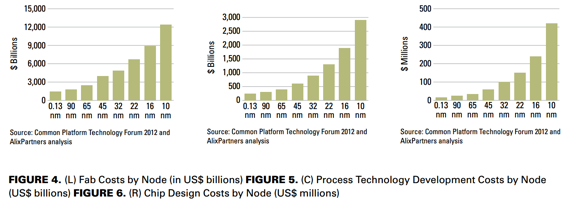

Since the 65 nm node, escalating costs of fab and process technology development and design, as illustrated in the chart below, put a huge pressure on the industry.

At the recent (2014) SST ConFab in Las Vegas Bill McClean shared his annual report on Major trends shaping the future IC Industry. Bill reports: “Over the last two decades, the percentage of capex being spent by the top 5 has steadily increased to its current 70% with the big three of Samsung, Intel and TSMC being responsible for over 50%.” This is illustrated by the following chart.

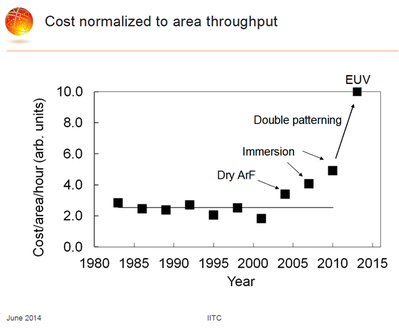

In the recent ITC conference Harry J. Levinson of GlobalFoundries in his talk: Lithography Issues for High Volume Manufacturing” presented the following chart:

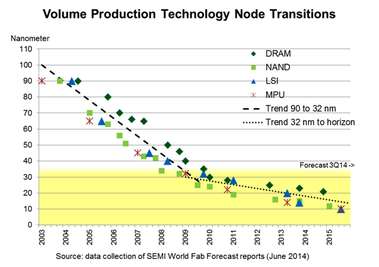

We should not be surprised that the production ramp up below 28 nm is extremely slow. There is too much money involved to put it into the wrong place.

Going back to the SEMI World Fab Forecast, the authors ask “What’s next?” and respond: “Many in our industry are grappling with what to do as they have perceived the coming slowdown in technology node transitions. IC manufacturers are now increasingly looking outside of conventional lithography and wafer size scaling approaches to pick up the pace of cost reduction while increasing transistor density and performance. Using memory as an example, to cope with increasing challenges in continuing to scale 2D, memory companies are looking into 3D.”

So the memory vendors already started shifting their Capex budget to scaling up with 3D NAND, instead of scaling to smaller dimension. Recently Qualcomm announced their collaboration with SMIC – China’s SMIC-Qualcomm 28-nm Deal: Why Now? – indicating more capacity build-up for 28 nm with looking forward to scaling up with monolithic 3D for logic as well. Quoting: ”Going forward, SMIC will also extend its technology offerings on 3DIC and RF front-end wafer manufacturing in support of Qualcomm”.

It is clear now that we are seeing a paradigm shift in the semiconductor equipment industry. After many decades of relentless dimensional scaling every two years, there is a change coming and we see a lower rate of dimensional scaling and exploration of other paths, to keep industry’s march on. We do believe that the next few decades will be about scaling with 3D Integration and we are pleased to see many others thinking the same.

The 2014 S3S Conference is scheduled for October 6-9, 2014, at the Westin San Francisco Airport, and would be a great opportunity to learn more about monolithic 3D technology, with five invited presentations covering topics from design tools to monolithic 3D NAND and other 3D memories. CEA Leti will present their work on CMOS monolithic 3D IC. Researchers from MIT and Stanford will present manufacturing monolithic 3D devices with materials other than silicon.

RSS Feed

RSS Feed