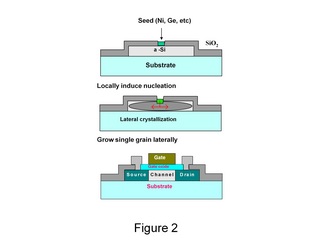

Saraswat in www.jbkempf.com/~jb/Post-CMOS/Stanford/Saraswat.ppt depicted the concept of multilayer Monolithic 3D with several “transistor levels” (Figure 1). Furthermore, he suggested to 1.nucleate and 2.crystallize amorphous silicon, forming the second level of transistors followed by another set of interconnect layers (Figure 2). Nucleating and crystallizing amorphous silicon turns to be a very difficult task especially when the chip has millions of transistors per level and when elevating the temperature could be detrimental. An alternative way is using TFTs on the second level of silicon, the problem with that is of course very poor performance of the transistors even after crystallization of the amorphous silicon to polycrystalline materials, as well as the need to generate S/D junctions at high temperature that will adversely affect the underlying devices.

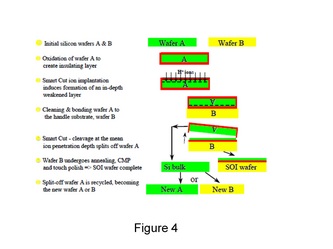

The other approach is integrating thin layer transfer onto a fully processed wafer, by that creating a second level of transistors, followed by a set of interconnect layers. The layer transfer is similar to the "smart-cut" process described by SOITEC in http://www.soitec.com/pdf/SmartCut_WP.pdf (Figure 4).

Applying layer transfer technology along with MonolithIC 3D Inc.’s IP portfolio is a new and fresh way to build the next generation of 3D device integration.

RSS Feed

RSS Feed