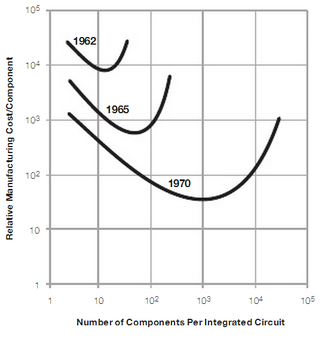

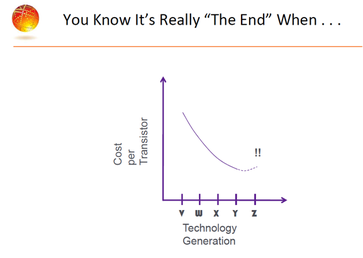

Let’s go back to 1965 and Moore’s paper in "Electronics, Volume 38, Number 8, April 19, 1965 The future of integrated electronics". The following figure represented Dr. Moore’s observation with regard to three consecutive technology nodes. Quoting: ..."the cost advantage continues to increase as the technology evolves toward the production of larger and larger circuit functions on a single semiconductor substrate. For simple circuits, the cost per component is nearly inversely proportional to the number of components, the result of the equivalent piece of semiconductor in the equivalent package containing more components. But as components are added, decreased yields more than compensate for the increased complexity, tending to raise the cost per component. Thus there is a minimum cost at any given time in the evolution of the technology"

a. The 28nm node is quite mature and we cannot expect that optimum integration vs. yield will double for it.

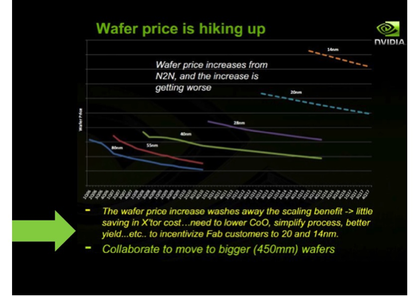

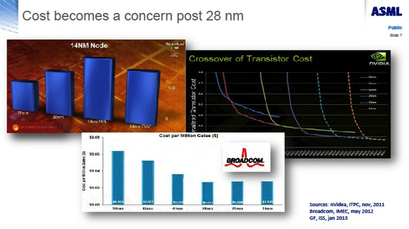

b. All that we know about the more advanced nodes (22/20nm, 16/14nm, …) indicates that the cost per transistor is not going to be reduced significantly vs. that of 28nm.

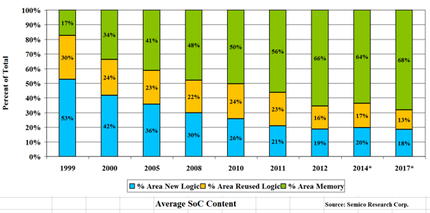

c. What we now know about embedded SRAM (“eSRAM”), I/O and other analog functions, indicates that most SoCs will end up at a higher cost as compared to 28nm.

Let’s recap using a few public charts to help tell the story of how we have reached that conclusion.

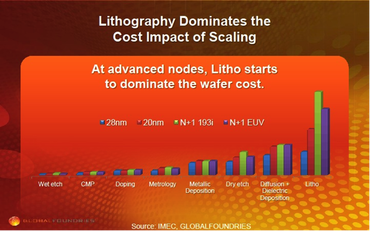

It starts with the escalating cost of lithography as illustrated in this 2013 chart from GlobalFoundries:

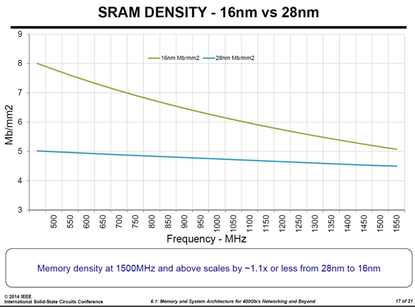

The following chart was presented in an invited paper by Dinesh Maheshwari, CTO of Memory Products Division at Cypress Semiconductors, at ISSCC2014. It was also at the center of our recent blog “Embedded SRAM Scaling is Broken and with it Moore’s Law.”

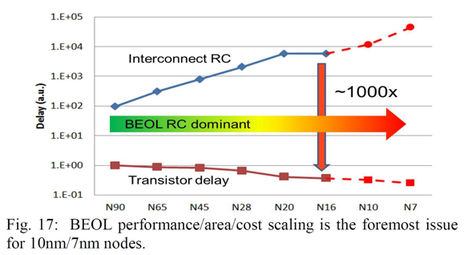

Final note: it seems clear that dimensional scaling has now reached negative returns, as is illustrated by the following GlobalFoundries chart:

RSS Feed

RSS Feed