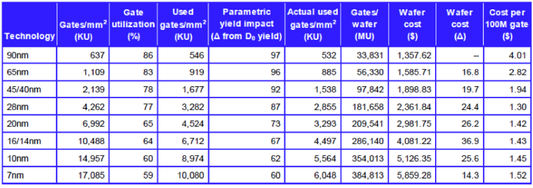

Our march 2014 blog Moore’s Law has stopped at 28nm! has recently been re-confirmed. At the time we wrote: “From this point on we will still be able to double the amount of transistors in a single device but not at lower cost. And, for most applications, the cost will actually go up.” This reconfirmation can be found in the following IBS cost analysis table slide, presented at the early Sept FD-SOI event in Shanghai.

As reported by EE Times - Chip Process War Heats Up, and quoting Handel Jones of IBS “28nm node is likely to be the biggest process of all through 2025”.

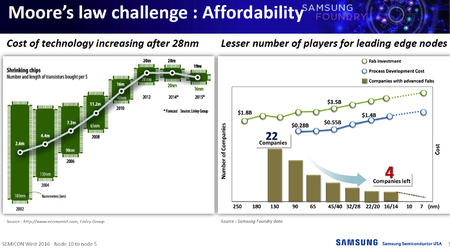

IBS prediction was seconded by “Samsung executive showed a foil saying it believes 28nm will have the lowest cost per transistor of any node.” The following chart was presented by Samsung at the recent Semicon West (2016).

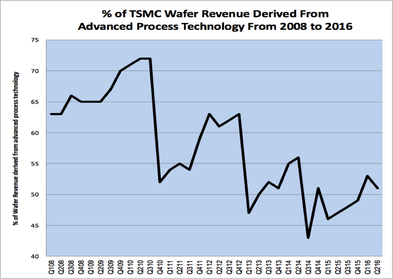

This discussion seems academic now, as the actual engineering costs of devices in advanced nodes have shown themselves to be too expensive for much of the industry. Consequently, and as predicted, the industry is bifurcating, with a few products pursuing scaling to 7nm while the majority of designs use 28nm or older nodes.

The following chart derived from TSMC quarterly earnings reports was published last week by Ed Sperling in the blog Stepping Back From Scaling:

This is good news for innovation, as a diversity of choices helps support new ideas and new technologies such as 3D NAND, FDSOI, MEMS and others. These technologies will enable new markets and products such as the emerging market of IoT.

A good opportunity to learn more about these new scaling technologies is the IEEE S3S ’16, to be held in the Hyatt Regency San Francisco Airport, October 10th thru 13th, 2016. It starts with 3D and FDSOI tutorials, the emerging technologies for the IC future. CEA Leti is scheduled to give an update on their CoolCube program, Qualcomm will present some of their work on monolithic 3D, and three leading researchers from an imec, MIT, and Korea university collaboration will present their work on advanced monolithic 3D integration technologies. Many other authors will discuss their work on monolithic 3DIC and its ecosystem, in addition to tracks focused on SOI, sub-VT and dedicated sessions on IoT.

RSS Feed

RSS Feed