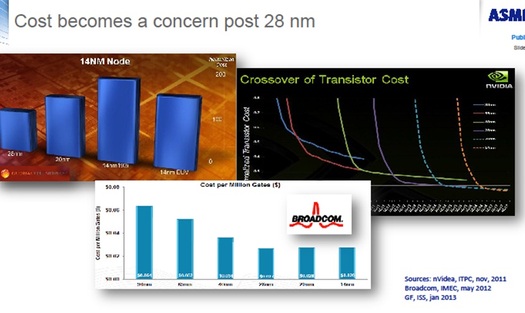

And 20% might be a conservative number once the dynamics of the last 30 years would hit a hard stop.

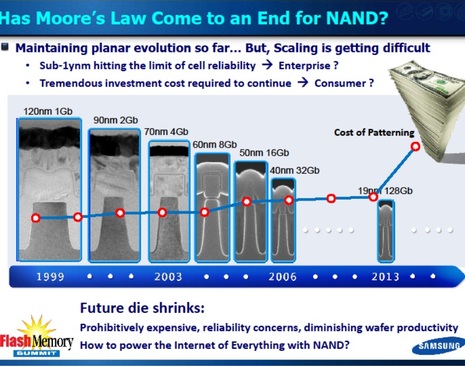

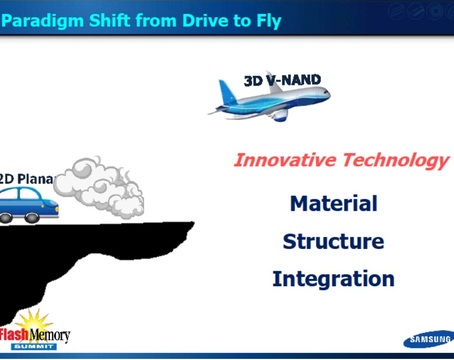

The following Samsung chart is a good illustration of where we are and the choice that at least Samsung has made:

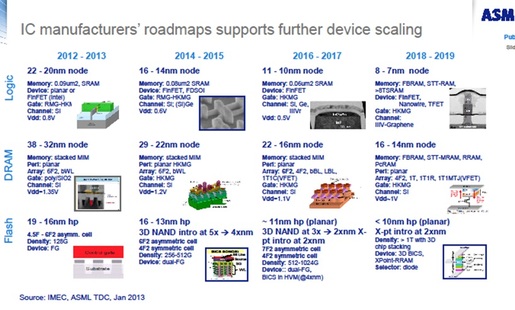

Samsung, Toshiba and the rest of the NAND industry are already taking action. On the SoC side the challenges are as severe, yet at this point the industry is consumed by the enormous efforts to bring up FinFETs. It may even bring up compound semiconductors (III-V) for the next node (10nm), but then what? At what cost? For what kind of return?

It seems to me that the right moves are:

First, logic design market needs to adopt an alternative to the embedded memory. IBM stated at the recent Common Platform Forum that adopting eDRAM gave it the equivalent benefit of one node scaling. This was seconded by Intel’s recent announcement of integrating eDRAM with their new Haswell processor - Intel eDRAM attacks graphics in pre-3-D IC days. An even better option would be the one transistor two state memory breakthrough solution recently developed by Zeno Semiconductors.

Second, logic design needs to follow the NAND industry by developing monolithic 3D technology for SoC and logic products. In a recent blog we reported that CEA Leti has placed Monolithic 3D is now on the roadmap for 2019. We are pleased to announce that we will provide a tutorial on monolithic 3D as a part of the upcoming IEEE 3D IC Conference in early October in San Francisco, and we will follow with a plenary talk the following week at the IEEE S3S Conference in Monterey. In these conferences we also plan to present a new practical process flow for monolithic 3D, leveraging industry’s shift to laser annealing. This technology supports 3D technologies we had presented in the past, and can be used independently for new monolithic 3D process flows. We are looking forward to meeting you all there.

RSS Feed

RSS Feed