Last week, during a dinner conversation with colleagues, the topic of scaling limits came up. Hmmm... I thought. Let me study this issue.

Prevailing Opinion

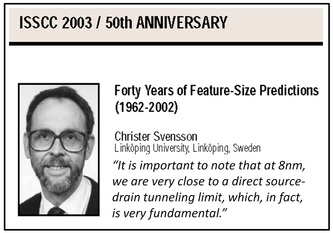

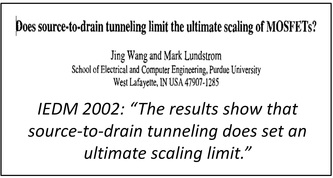

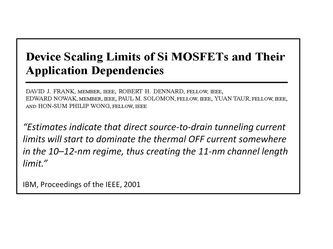

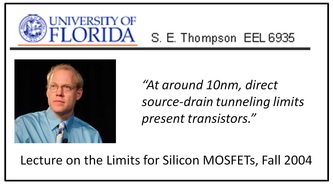

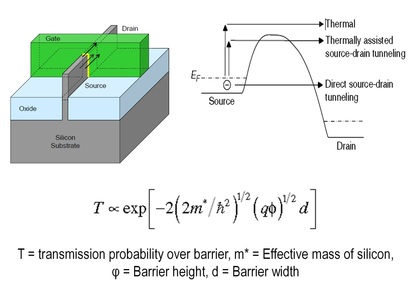

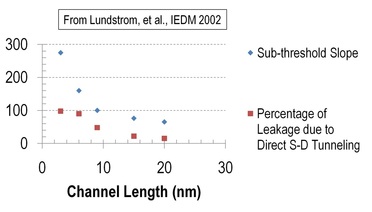

CMOS scaling limits have been a much researched issue. Figure 1 is a summary of analyses from various well-known folks in the semiconductor community. They all believe direct source-drain tunneling is the fundamental limiter to MOSFET feature-size scaling. These analyses were presented in top forums in our industry, such as the International Solid State Circuits Conference (ISSCC), the International Electron Devices Meeting (IEDM) and the Proceedings of the IEEE.

When a transistor is OFF, there exists a potential barrier between the source and the drain, as shown in Figure 2. Leakage in present-day (22nm channel length) transistors is predominantly thermal assisted. For really small channel lengths (<10nm) though, one could have direct quantum-mechanical tunneling from the source to the drain. Figure 2 shows an equation for direct source-drain tunneling, which depends on:

- Width of the barrier, which is the channel length

- Height of the barrier, and

- Effective mass of carriers, which is a property of the transistor material

Is CMOS transistor miniaturization going to end around the 5nm node, or is there a way out?

Those of us working on semiconductors and chip design know most problems in our field can be solved, however daunting they might appear at the beginning. I spent some time thinking about the direct source-drain tunneling problem last week, and believe there is a solution. We may be able to scale CMOS logic transistors beyond the 5nm node, and it doesn't require any rocket science. Let me show you how...

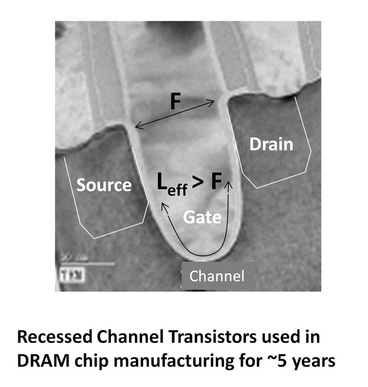

Around the 90nm node, the DRAM industry had to figure out ways to reduce transistor feature sizes without running into leakage limitations. They started using an interesting device structure called a recessed channel MOSFET (Figure 4). In this device, the effective channel length is longer than the minimum feature size. For example, at the 90nm node, the transistor's effective channel length could be 180nm. So, one gets the density benefits of scaled feature sizes, and at the same time, leakage issues, which are crucial to DRAM, are avoided. Samsung, Hynix and Micron have manufactured this device for DRAM chips for around 5 years now. At the 2003 Symposium on VLSI Technology, Samsung reported that these devices offered 10x lower leakage, similar drive currents and higher gate capacitance compared to planar transistors. The chances are that you own a billion of these recessed channel devices, and are using them for the DRAM of your computer!

Conclusion: It certainly looks like we might be able to miniaturize CMOS technologies beyond the 5nm node someday.

Caveats

My conclusion above comes with a few caveats:

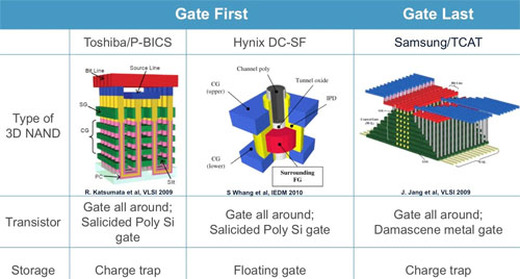

- NAND flash memory manufacturers such as Toshiba, Samsung and Micron scale the fastest in our industry. Due to the litho challenges they've hit, these companies are looking at alternative ways to get the benefits of scaling without lowering feature sizes. They've identified monolithic 3D as one way to do this (Figure 5). In fact, I hear one of these manufacturers is buying tools from equipment vendors to go to risk production with monolithic 3D in 2-3 years time! It remains to be seen whether similar approaches will be adopted for logic. If so, the logic industry may not need to move beyond the 5nm node in the next two decades.

- Notice how I said we may cross the 5nm node someday in my statement above. I did not say we would cross it with a 2 or 3 year cadence. This is mainly due to issues with lithography. ASML has more than 75% market share in immersion lithography and has a dominant position in EUV too. Having (almost) a sole supplier situation for what is probably the most important part of our industry is unfortunate. A sole supplier, due to lack of competition, can charge huge prices for his tools and is not penalized (much) for delayed product launches. Israel Beinglass' recent blog-post talked about ASML's revenue growing much faster than the rest of the equipment industry due to their high tool prices. Lack of competitive, timely and affordable litho technology can cause Moore's Law to slow down or can cause manufacturers to complement feature size scaling with approaches such as monolithic 3D.

- Devices such as recessed channel transistors or vertical transistors form just one possible solution to the direct source-drain tunneling issue. Other (possibly better) solutions could exist. The key point is that the direct source-drain tunneling limit may not be as fundamental as we think.

RSS Feed

RSS Feed