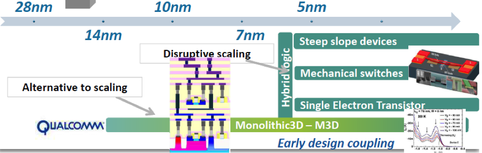

Most in the industry are in agreement that scaling past the 22nm node, while still quite technically feasible, has priced itself out of most markets. Olivier discussed the what (transistor costs are no longer decreasing) and the why (litho cost escalation and connectivity inefficiencies of energy and delay). And then he made the statement: “if we just keep the current (2Xnm) technology, we can go farther in cost scaling.” [note: see the following blogs and comments for more info on this crucial topic: Tech Design Forums summary "3D and EDA need to make up for Moore’s Law, says Qualcomm" and Zvi-Or-Bach’s EETimes blogs Qualcomm Calls for Monolithic 3D IC and 28nm - The Last Node of Moore's Law.]

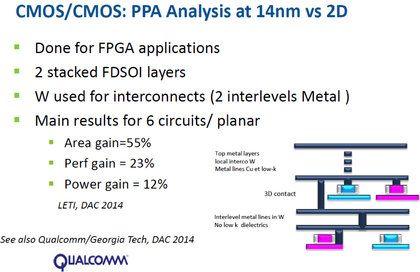

Oliver showed a summary of a DAC2014 paper and a Qualcomm/GeorgiaTech DAC2014 paper Power/Performance/Area analysis of M3D for an FPGA:

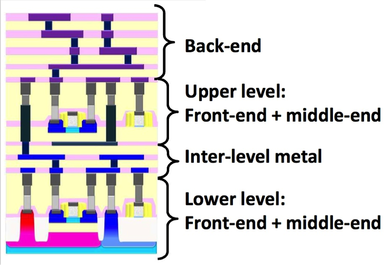

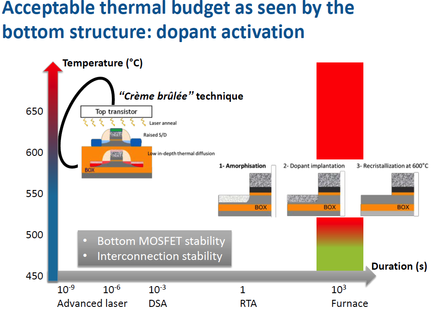

Now upper-level transistors are formed utilizing SPER (Solid Phase Epitaxial Regrow) for junction doping at 475-600°C and other lower (<400°C) temperature processing for gate stacks, etc. The upper-level and inter-level vertical interconnect is then processed, again with full alignment capability to the lower layer. Note that the lower level transistor Ni salicides are stabilized with platinum co-deposition and fluorine/tungsten implantation to enable their survival at the 475-600°C SPER thermal exposure.

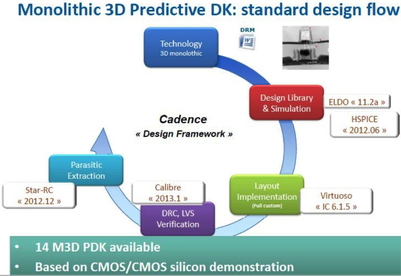

Leti has a 14nmPDK ready to go for those who want to design a test circuit in their monolithic 3D flow. They have ELDO, HSPICE, Virtusoso, Calibre, StarRC, etc. files available.

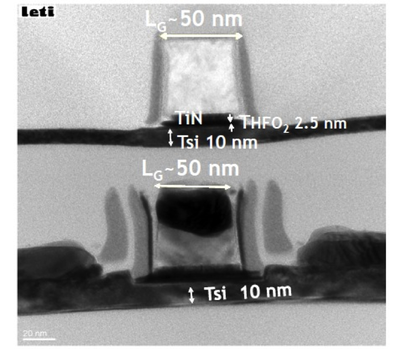

CEA-Leti has been busy working on processing flows to enable monolithic 3D devices since before 2009. Perrine Batude won the 2009 Roger A. Haken Best Student Paper Award for the IEDM 2009 paper entitled, “Advances in 3D CMOS Sequential Integration,” where she showed results for a sequentially processed P over N (no metal between transistors layers) testchip Batude’s 2011 IEDM paper showed a 50nm 3D sequential structure on 10nm channel silicon:

Clearly, monolithic 3D integration has a very important role for the future of the semiconductor industry. I would like to invite you to the IEEE S3S Conference: SOI technology, 3D Integration, and Subthreshold Microelectronics. The 2014 S3S Conference will be held October 6-9, 2014 at the Westin San Francisco Airport. This would be a great opportunity to learn more about monolithic 3D technology, with five invited presentations covering topics from design tools to monolithic 3D NAND and other 3D memories. CEA Leti will present their work on CMOS monolithic 3D IC. Researchers from MIT and Stanford will present manufacturing monolithic 3D devices with materials other than silicon.

See you there!

RSS Feed

RSS Feed