A technology that could bridge the processor memory gap, Monolithic 3D has DARPA's attention. The agency wants proposals by Nov 6. Learn more at an upcoming IEEE conference.

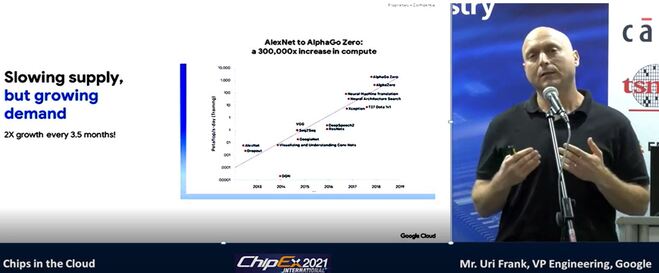

Among those is the 3DSoC program. “The overall goal of the Three Dimensional Monolithic System-on-a-Chip (3DSoC) program" DARPA wrote in a statement, "is to develop 3D monolithic technology that will enable > 50X improvement in SOC digital performance at power. 3DSoC aims to drive research in process, design tools, and new compute architectures for future designs while utilizing U.S. fabrication capabilities.” As is illustrated in the following chart:

The underlying problem enabling these orders of magnitude improvement is often called “The Memory Wall” illustrated by the following chart from Hennessy and Patterson:

DARPA kept the target enhancement to only 50x to allow use of chip manufactured in domestic older fab (~90nm) instead of off-shore 7nm fab lines.

Proposals are due by Nov 6, allowing everyone a unique opportunity to hear an invited talk about the program on October 16 from the 3DSoC DARPA Program Manager, Dr. Linton Salmon during this year’s IEEE S3S 2017 at the Hyatt Regency at the San Francisco Airport. The IEEE S3S conference is dedicated to monolithic 3D technologies. It provides unparalleled opportunity for quick catch up with the broad spectrum of monolithic technologies.

At the conference’s start Al Fazio, Intel Senior Fellow, will deliver a plenary talk on how 3D NAND and 3D XPoint ended being the trailblazing monolithic 3D IC technologies that have matured to volume production, taking over the fast growing memory market. The first day will conclude with two 3D IC focus sessions comprised of a mix of invited and submitted papers covering exotic technologies and the use of the emerging nano-wire transistors for 3D scaling.

The first half of the second day includes a collaborative event organized by Qualcomm and CEA Leti — the COOLCUBE/3DVLSI Open Workshop. The second half includes an open 3D tutorial providing full coverage of the various 3D integration technologies from TSV to Sequential Integrations.

The third day is made of four sessions of invited and submitted talks on monolithic and other forms of 3D integration. These sessions include a talk by MonolithIC 3D Inc. in which we will present a monolithic 3D technology that is ready to be rapidly deployed using the current transistor process. We will also describe how such an integration technology could be used to improve performance, reduce power and cost of most computer systems, suggestive of a 1,000x total system benefit.

In addition, the IEEE S3S conference includes full coverage of SOI and low-power technologies, making it the place to be and to learn about alternative technologies to dimensional scaling. I am looking forward to seeing you at the S3S from October 16th thru 19th, 2017.

RSS Feed

RSS Feed