The first one is the IEEE International Conference on 3D System Integration (3D IC), October 2-4, 2013 in San Francisco, and just following in the second week of October is the S3S Conference on October 7-10 in Monterey. The IEEE S3S Conference was enhanced this year to include the 3D IC track and accordingly got the new name S3S (SOI-3D-Subthreshold). It does indicate the growing importance and interest in 3D IC technology.

This year is special in that both of these conferences will contain presentations on the two aspects of 3D IC technologies. The first one is 3D IC by the use of Through -Silicon-Via which some call -”parallel” 3D and the second one is the monolithic 3D-IC which some call “sequential.”

This is very important progress for the second type of 3D IC technology. I clearly remember back in early 2010 attending another local IEEE 3D IC Conference: 3D Interconnect: Shaping Future Technology. An IBM technologist started his presentation titled “Through Silicon Via (TSV) for 3D integration” with an apology for the redundancy in his presentation title, stating that if it 3D integration it must be TSV!

Yes, we have made quite a lot of progress since then. This year one of the major semiconductor research organization – CEA Leti – has placed monolithic 3D on its near term road-map, and was followed shortly after by a Samsung announcement of mass production of monolithic 3D non volatile memories – 3D NAND.

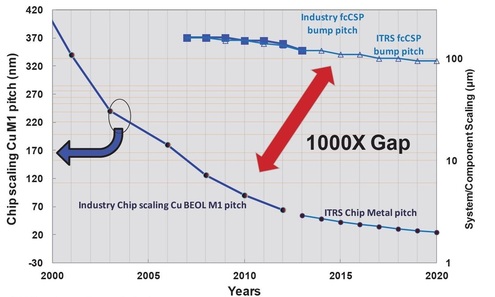

We are now learning to accept that 3D IC has two sides, which in fact complement each other. In hoping not to over-simplify- I would say that main function of the TSV type of 3D ICs is to overcome the limitation of PCB interconnect as well being manifest by the well known Hybrid Memory Cube consortium, bridging the gap between DRAM memories being built by the memory vendors and the processors being build by the processor vendors. At the recent VLSI Conference Dr. Jack Sun, CTO of TSMC present the 1000x gap which is been open between on chip interconnect and the off chip interconnect. This clearly explain why TSMC is putting so much effort on TSV technology – see following figure:

In the following S3S conference we are scheduled on October 8, to provide the 3D Plenary Talk for the 3D IC track of the S3S conference. The Plenary Talk will present three independent paths for monolithic 3D using the same materials, fab equipment and well established semiconductor processes for monolithic 3D IC. These three paths could be used independently or be mixed providing multiple options for tailoring differently by different entities.

Clearly 3D IC technologies are growing in importance and this coming October brings golden opportunities to get a ‘two for one’ and catch up and learn the latest and greatest in TSV and monolithic 3D technologies — looking forward to see you there.

RSS Feed

RSS Feed