We can still make transistors smaller but not cheaper

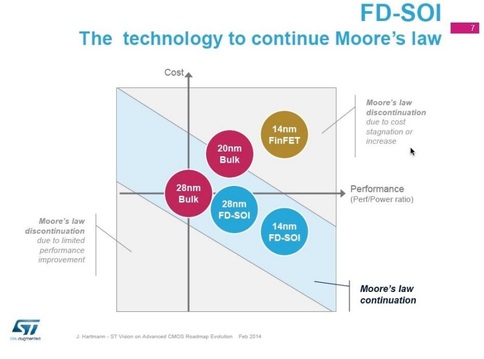

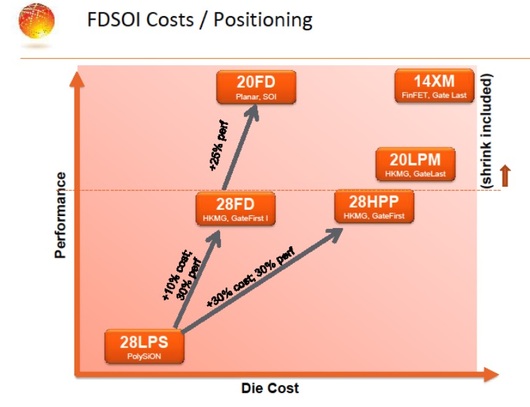

ST information is backed by Globalfoundries as we can see from the following chart presented at the 2013 SOI Consortium workshop in Kyoto, Japan.

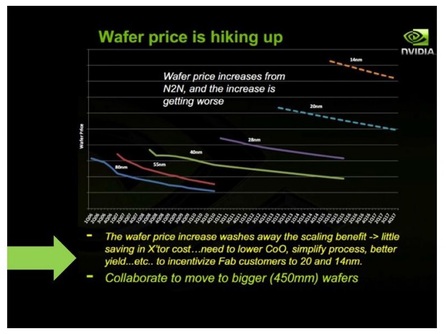

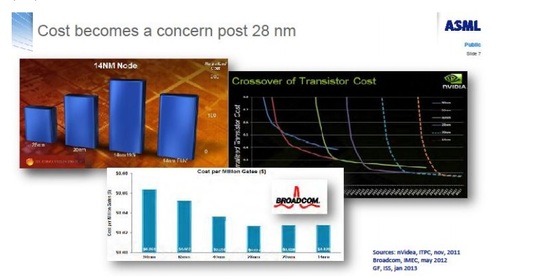

Beyond 28nm, scaling becomes extremely expensive due to double litho, HKMG, FinFET, etc. The increase in wafer cost is illustrated by the recent NVidia chart from Semicon Japan (Dec. 2013) below:

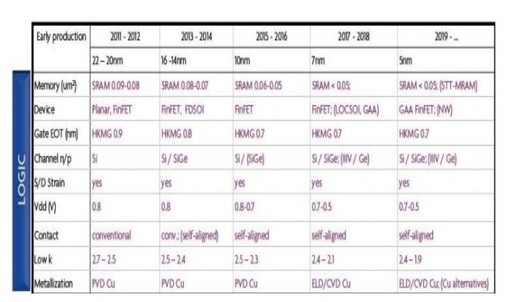

At 28nm the bitcell size is about 0.12µm². The following chart by imec reported in Status update on logic and memory roadmaps (Oct 2013):

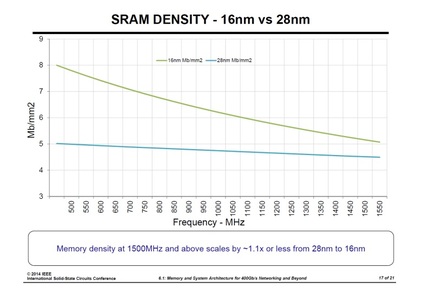

- Smaller transistors have less drive, thus requiring breaking the SRAM into smaller blocks, creating more overhead area costs

- Smaller transistors have a higher level of variation, also requiring breaking the SRAM into smaller blocks

- The need for more overhead such as read assist circuits and write assist circuits

- Tighter metal pitches begat higher RC, thus again requiring breaking the SRAM into smaller blocks

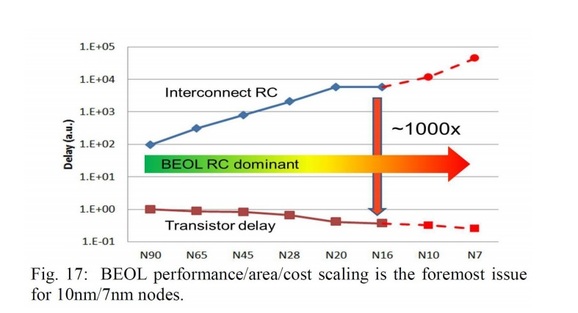

Furthermore, the exponential increase in BEOL RC as is illustrated by the following chart, presented by Geoffrey Yeap, VP of Technology at Qualcomm in his invited IEDM 2013 paper, results in an exponential increase of number of drivers and repeaters. This suppresses the effective gate density increase to only a factor of x1.6, or less.

As an industry, we are facing a paradigm shift because dimensional scaling is no longer the path for cost scaling. New paths need to be explored such as SOI and monolithic 3D integration. It is therefore fitting that the traditional IEEE conference on SOI has expanded its scope and renamed itself to IEEE S3S: SOI technology, 3D Integration, and Subthreshold Microelectronics. The 2014 S3S conference is scheduled for October 6-9, 2014 at the Westin San Francisco Airport. This new unified conference will help us to improve efficiency and establish this conference as a world class international venue to present and learn about the most up-to-date trends in CMOS and post-CMOS Scaling. The conference will provide both educational and cutting edge research in SOI and monolithic 3D and other supporting domains. These technologies were not part of the mainstream semiconductor past; accordingly, it is a golden opportunity to catch-up with these technologies now. Please mark your calendar for this opportunity to contribute and learn about SOI and monolithic 3D technology, as these technologies are well positioned to keep the semiconductor industry's future momentum.

RSS Feed

RSS Feed