Logic Gate Model

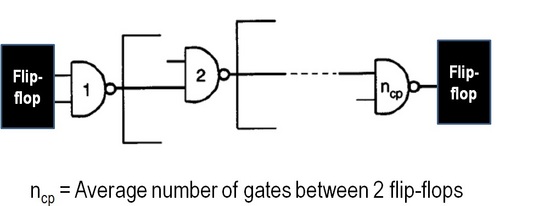

Fig. M4: Logic path model.

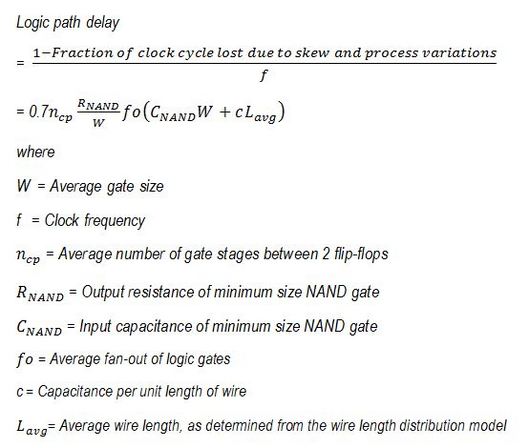

Logic gate paths are modeled as multiple stages of 2-input NAND gates between flip-flops, as shown in Fig. M4. An average length wire, whose length is determined from the wire length distribution model, exists between two NAND gate stages. NAND gate sizes are determined based on these conditions, using the equations shown in Fig. M5. While this is an approximate method to obtain logic gate sizes, area and power, it is simple and widely-used and is therefore adopted for IntSim v2.0. Please see [15][18] for more details of this model.

Fig. M5: Equations for determining average gate size.