Why MonolithIC 3D?

A number of research papers have estimated the benefits of 3D over the years:

- Die Stacking (ED) Microarchitecture - Intel's paper on their effort to simulate a Pentium 4 processor built in 3D. Their investigation showed that 3D stacking with two stacked die (even with fat TSVs) gave a 54% reduction in power and a 22C reduction in chip temperature for the same performance!

- Interconnect Limits on Gigascale Integration in the 21st Century - Paper from the groups of Profs. Meindl (Georgia Tech), Reif (MIT) and Saraswat (Stanford). They reported a 3x reduction in die size with four stacked die when monolithic 3D integration is used.

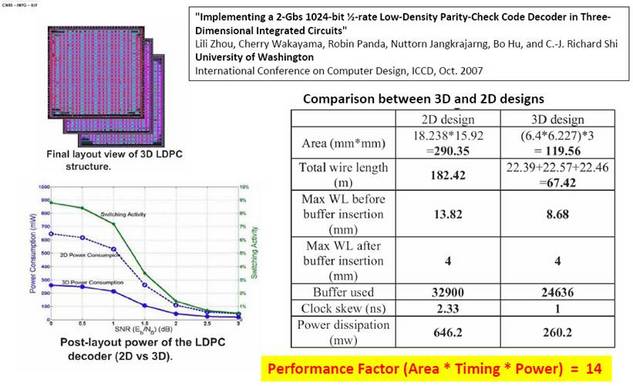

- Implementing a 2-Gbs 1024-bit ½-rate Low-Density Parity-Check Code Decoder in Three-Dimensional Integrated Circuits - A paper from the Univ. of Washington where they taped out a LDPC decoder in 3D - please see figure below. The improvement in the figure of merit (area*timing*power) is more than 10x.