Local Interconnect Model

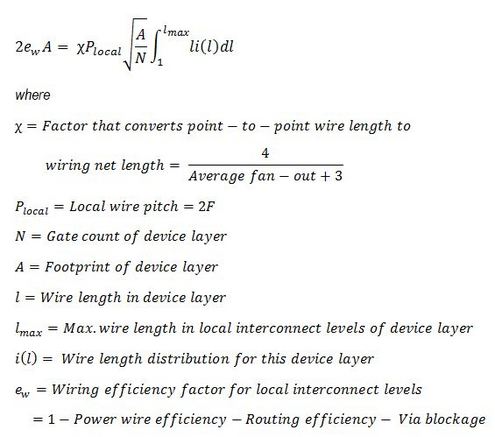

IntSim v2.0 has two metal levels for each device layer to route local signal, power and clock interconnect networks. These metal levels are also designed to remove heat from transistors in stacked device layers. Local interconnect pitch is selected as 2F, where F is the minimum feature size. Length of the longest signal wire routed in local interconnect levels is obtained from the equations shown in Fig. M11. Power wire efficiency is obtained from the local power grid model derived in [26] and also from considerations shown in the thermal models page. Via blockage to higher metal levels and via blockage due to repeaters are modeled using equations derived in [27].

Fig. M11: Local interconnect models.