3D Chip Cooling

It's easy to understand why heat removal is an issue for 3D: if you stack two chips of power density PD atop each other, the net power density doubles and becomes 2*PD. Furthermore, one of the chips is far away from the heat sink, making heat removal even more difficult. Several solutions to this problem exist and are summarized below.

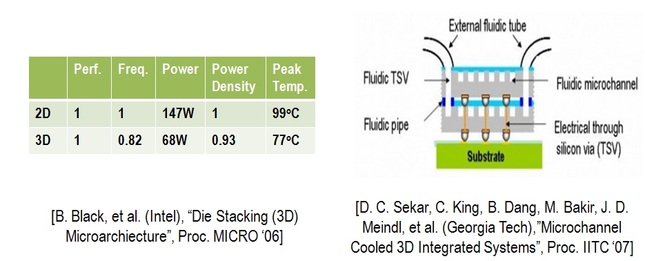

(1) A few years back, Intel simulated the impact of building a Pentium 4 processor in 3D (link to paper). Their results are summarized in the above table. Wire delay between multiple functional blocks (eg. between the cache and various functional blocks) reduced significantly due to 3D stacking. This allowed them to reach their target performance at lower clock frequency, which in turn reduced power consumption from 147W to 68W. The Intel team had a detailed thermal model for the 2-die logic-on-logic 3D stack, and showed that peak temperature is manageable, since they placed high-power functional units atop low-power functional units.

(2) CAD tools have been developed that place circuits/blocks in 3D to minimize total wire length (for example) under the constraint of temperature being <85C. This automates and improves the procedure the Intel team used - namely placing high-power cells/circuits above low-power ones. Furthermore, these CAD tools add "thermal vias" in power-hungry sections of the 3D stack to reduce temperature. Jason Cong (UCLA), Guojie Luo (UCLA) and Yiyu Shi (previously UCLA, now U. of Missouri) have done some nice work in this area.

(3) MonolithIC 3D Inc. is collaborating with Stanford University on a novel heat removal solution for 3D dice. We hope to publish these results in the near future - will write a blog post when this exciting idea becomes public.

(4) Georgia Tech has been working on a liquid cooling technique for 3D stacked dice. Liquid was passed on the back-side of each die in the 3D stack (see picture above), and one could cool even power-hungry 100W-type chips stacked in 3D. Note that these liquid cooling solutions have a long-term scope...

So, what's the bottom line?

We should be able to cool sub-1W chips used for portable applications such as cell-phones, smart-phones and tablet computers when they're stacked in 3D. In fact, these types of chips are being 3D stacked even today to save space in cell-phones. Portable applications are projected to be the growth and volume drivers for the semiconductor industry for the next 10 years, and we believe they will drive adoption of 3D technology.

Our analysis shows 20W-class chips used for laptops can be cooled on 3D stacking using techniques such as (1), (2) and (3). The biggest challenge for 3D is cooling 100W-class chips used for servers and desktops... while a liquid cooling solution can potentially handle this in the long-term, we're hoping to handle this in the short-term using design techniques similar to the ones described above.