**Technology Breakthrough**

# <u>A Microdisplay with 1/10<sup>th</sup> the Power, 1cm<sup>3</sup> Volume, 10g Weight</u> <u>and Far Fewer Components</u>

### 1000x1000 Pixels Micro-Display ~ 1cm<sup>2</sup>

#### **Technology:**

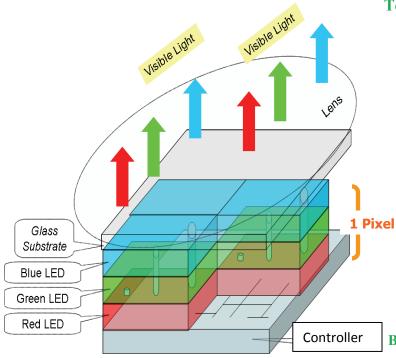

The monolithic 3D IC technology is extended by using a novel architecture with stacked RGB LEDs. This architecture avoids filters, polarizers and LCD layers when compared to today's displays. This, combined with efficient color-tunable RGB LEDs, provides an order of magnitude lower power consumption.

Key Features:

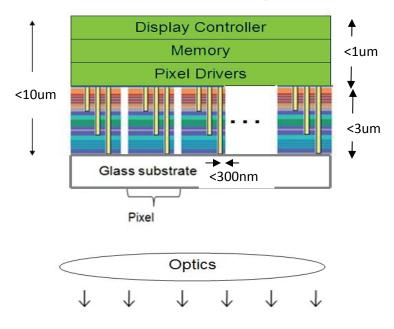

- Vertical interconnect pitch <300nm</li>

- ➤ Thickness of stacked regions<10µm</p>

See reverse side for more on monolithic 3D IC technology

#### **Benefits:**

- > 8x-10x lower power consumption

- Dramatic reduction in cost since fewer components

- Display is constructed by dividing LED area into multiple pixels

#### **Applications:**

- Rugged heads-up displays

- > Ultra-low power pico projectors

- > Bright high-resolution hand held

- ▶ Mobile displays up to 10<sup>6</sup>pixels/mm<sup>2</sup>

- > Flexible high bandwidth light pulse signaling

- Cockpit illumination

- > Map lights

**Technology Breakthrough**

## <u>Layer Transfer Technology ("Ion-Cut")</u> Defect-free single crystal obtained @ <400°C

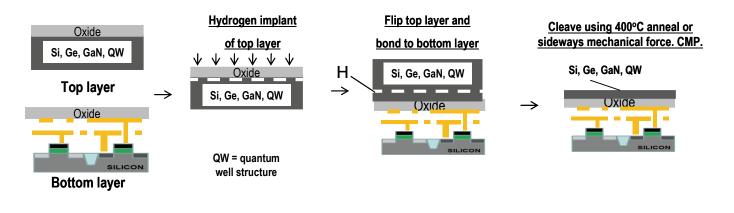

Leveraging a mature technology (wafer bonding and ion-cleaving) that has been the dominant SOI wafer production method for over two decades.

**Innovate and create** multiple thin (10s – 100s nanometer scale) layers of virtually defect free Silicon, Germanium, Gallium Nitride, and quantum well structures by utilizing low temperature (<400°C) bond and cleave techniques, and place on top of active transistor circuitry. Benefit from a rich layer-to-layer interconnection density.

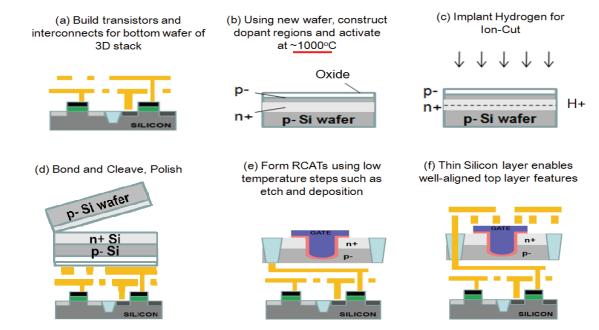

**Create** a layer of Recessed ChAnnel Transistors (RCATs), commonly used in DRAMs, by activating dopants at  $\sim 1000^{\circ}$ C **before** wafer bonding to the CMOS substrate and cleaving, thereby leaving a very thin dopant stack layer from which transistors are completed, utilizing less than 400°C etch and deposition processes.

• MonolithIC 3D<sup>™</sup>, Inc. ◆ 3555 Woodford Dr ◆ San Jose, CA 95124 ◆ Tel. 408-372-7101 ◆ Fax. 408-912-2303 www.monolithic3d.com. ◆Patents pending