The International Magazine for the Semiconductor Packaging Industry

Volume 17, Number 1

January - February 2013

**Cover Feature**

# A PoP for the Post-PC Era

Page 30

- Supply Chains for HVM of 3D IC integration

- Cost Efficient Wafer-Level Stacking Technologies

- Functional Testing of 0.3mm-pitch WLPs to Multi-GHz Speed

- Spring Probes/ Probe Cards: Wafer-Level Test as Full Functional Test

### Solid State Equipment LLC

ADVANCED PACKAGING SINGLE WAFER WET PROCESSING

### TSV RESIST STRIP AND CLEAN

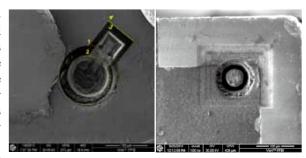

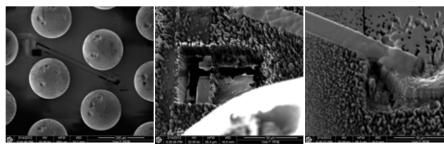

$\label{eq:As received} \textbf{As received} - \textbf{post DRIE}$

After SSEC Cleaning

As received - post DRIE

After SSEC Cleaning

As received - post DRIE

After SSEC Cleaning

### Si ETCH TO REVEAL Cu TSV

Optical

SEM

ISIS 3D

### DRY FILM STRIP

### **FLUX CLEANING**

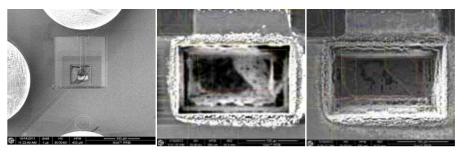

### UBM AND RDL METAL ETCH

UBM Post Etch

UBM Post Strip

## CONTENTS

### January February 2013 Volume 17, Number 1

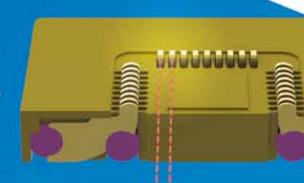

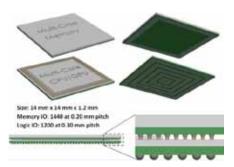

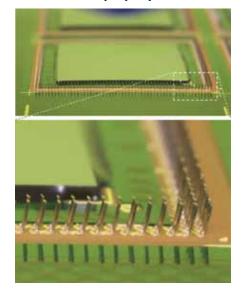

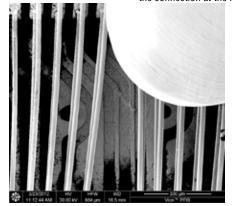

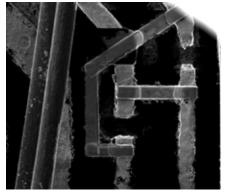

The cover photo shows Bond Via Array<sup>TM</sup> (BVA<sup>TM</sup>)

PoP technology from Invensas. It enables 1000+

memory-logic IO utilizing free-standing wire

structures in lieu of TSVs. The technology addresses

the industry's need for increasing the performance of

processor-memory interconnect as it transitions from

single core to multi-core CPUs, while also handling

the requirements of low-power computing and cloud

computing. It can be used in applications such as 3D

packaging, embedded packaging, and WLP.

The International Magazine for Device and Wafer-level Test, Assembly, and Packaging Addressing High-density Interconnection of Microelectronic IC's including 3D packages, MEMS, MOEMS, RF/Wireless, Optoelectronic and Other Wafer-fabricated Devices for the 21st Century.

### **FEATURE ARTICLES**

| Cost Efficient Wafer-Level Stacking Technologies Mariam Sadaka, Soitec USA, Ionut Radu, Chrystelle Lagahe-Blanchard, Soitec France, Lea Di Cioccio, CEA-Leti | 24 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A PoP for the Post-PC Era Ilyas Mohammed, Invensas Corporation                                                                                               | 29 |

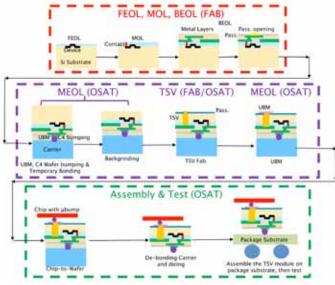

| Supply Chains for High-Volume Manufacturing of 3D IC Integration John H. Lau, <i>ITRI</i>                                                                    | 33 |

| Wafer-Level Test as Full Functional Test Increases Requirements for Spring Probes and Probe Cards  James Brandes, Christopher Cuda, Multitest                | 40 |

## FLIPCHIP BONDER

### BEST QUALITY, HIGHEST THROGHTPUT, FIELD PROOVEN RELIABILITY

- Anti vibration design for high reliability

- Best bonding accuracy by high performance of vision system

- Flux residue inspection function at flux plate

■ Thin die bonding capability as thin as 50µm

**MODEL: FLIPCHIP BOND-A110**

### SPECIFICATION

| PRODUCTIVITY UPH        |                             | ea | 10,000                       |

|-------------------------|-----------------------------|----|------------------------------|

| PRECISION X-Y PLACEMENT |                             | μm | ±6.0 @ 3σ                    |

|                         | CHIP ROTATION               | θ  | ±0.1° @ 3σ                   |

| BONDING HEAD            | BONDING FORCE               | N  | 1 ~ 20(PROGRAMMABLE FROM 1N) |

| UTILITIES               | MACHINE SIZE(W $x$ D $x$ H) | mm | 1,730 x 1,200 x 1,500        |

|                         | MACHINE WEIGHT              | Kg | 2,500                        |

|                         | Min. DIE SIZE               | mm | 0.5 x 0.5                    |

|                         | THIN DIE HANDLING           | μm | 50                           |

#532-2, Gajwa-Dong, Seo-Gu, Incheon, 404-250, Korea TEL: +82-32-571-9100 FAX: +82-32-571-9101 www.hanmisemi.com

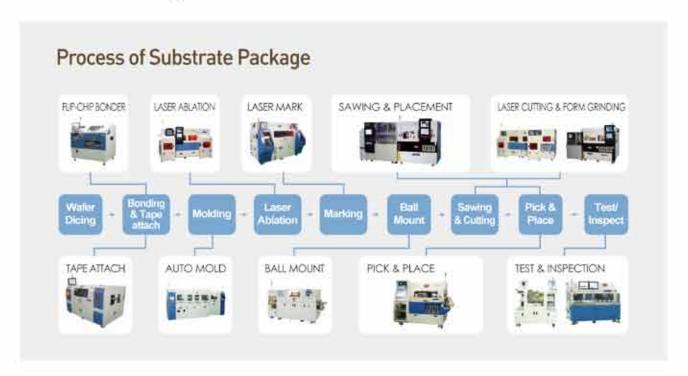

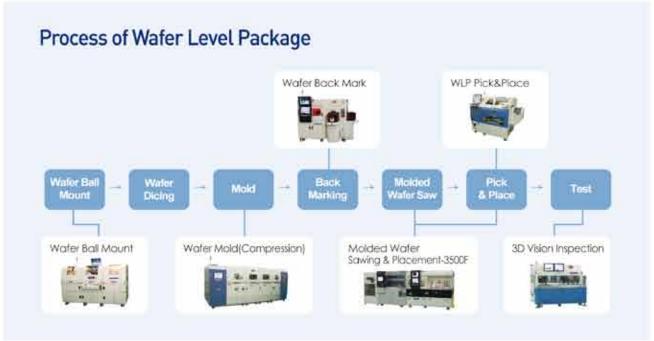

## Provides the best solution for all semiconductor packages

Leading the trend of semiconductor packages, HANMI is supplying the equipment not only for substrate packages but for wafer level packages. We are now developing the equipment to support new advanced technology such as TSVs.

## reduce soft errors

Deliver more density on your IC packages without soft errors.

Honeywell RadLo™ low alpha packaging materials help eliminate soft errors and single event upsets by reducing alpha emissions, a significant source of these problems. This is becoming increasingly important as chip dimensions and designs continue to miniaturize. Our leadership

and expertise in low alpha refining and metrology mean that Honeywell can help you meet critical alpha emission levels.

Honeywell reliability. Reliable low alpha. Make sure to ask your suppliers if they are using Honeywell RadLo low alpha materials for their chip packaging processes.

## **Honeywell**

Find out more by visiting us at www.honeywell-radlo.com

### **FEATURE ARTICLES**

| Package-Level Circuit Modifications Using Plasma-FIB to Create Functional Prototypes Peter Carleson, Brian Routh Jr., Trevan Landin, Kenny Mania, FEI Company | 44 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Functional Testing of 0.3mm-pitch Wafer-Level Packages to Multi-GHz Speed Ila Pal, Ironwood Electronics                                                       | 48 |

### **DEPARTMENTS**

| 4 | From the Publisher<br>Kim Newman, <i>Chip Scale Review</i>                                                                                                         | 6  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Market Trends Global Economy Drives the IC Industry's Cycle Bill McClean, IC Insights, Inc.                                                                        | 8  |

|   | Guest Editorial Requirements: Aren't They Obvious? David Barnum, Sensata Technologies                                                                              | 13 |

|   | MEMS Guest Editorial Robust Process Solutions for MEMS Flip-Chip Applications With Medium Density Lead-Free Solder Interconnects  Dave DiPaola, DiPaola Consulting | 15 |

|   | Industry News<br>Chip Scale Review Staff                                                                                                                           | 19 |

|   | Interview Growing Up in Tough Times Chip Scale Review Staff                                                                                                        | 50 |

| S | Product News<br>Chip Scale Review Staff                                                                                                                            | 52 |

| y | Advertiser Index, Advertising Sales                                                                                                                                | 56 |

- For 6"~12", 50 µm thin to standard wafers; warped, bumped or perforated

- Compatible with standard cassette, FOUP & horizontal shipping box

- Side supporting rails maintain stability and permit safe wafer flipping

For datasheet, please contact info@wafer-handling.com | Also visit www.wafer-handling.com to see our complete line of products for wafer handling automation

P +1.408.200.8345 | F +1.408.200.8341 | 2343 Bering Drive, San Jose, CA 95131, USA

Volume 17, Number 1

The International Magazine for Device and Wafer-level

Test, Assembly, and Packaging Addressing

High-density Interconnection of Microelectronic IC's

including 3D packages, MEMS, MOEMS,

RF/Wireless, Optoelectronic and Other

Wafer-labricated Devices for the 21st Century.

#### STAFF

Kim Newman Publisher knewman@chipscalereview.com Lawrence Michaels Managing Director

lxm@chipscalereview.com

**Debra Vogler** Senior Technical Editor dvogler@chipscalereview.com

**Dr. Thomas Di Stefano** Contributing Editor tom@centipedesystems.com

**Jason Mirabito** Contributing Legal Editor mirabito@mintz.com

Paul M. Sakamoto Contributing Editor Test paul.sakamoto@comcast.net

Sandra Winkler Contributing Editor slwinkler@newventureresearch.com

#### **EDITORIAL ADVISORS**

Dr. Andy Mackie (Chair) Indium Corporation

Rolf Aschenbrenner Fraunhofer Institute

Dr. Thomas Di Stefano Centipede Systems

Joseph Fjelstad Verdant Electronics

Dr. Arun Gowda GE Global Research

Dr. John Lau Industrial Tech Research Institute (ITRI)

Nick Leonardi Premier Semiconductor Services

Dr. Alan Rae Alfred Technology Resources

Dr. Ephraim Suhir ERS Company

Dr. Venky Sundaram Georgia Institute of Technology3D Systems Packaging Research Center

Fred Taber BiTS Workshop

Francoise von Trapp 3D InCites

Dr. C.P. Wong Georgia Institute of Technology

#### **SUBSCRIPTION INQUIRIES**

Chip Scale Review T 408-429-8585 F 408-429-8605 subs@chipscalereview.com

Advertising Production Inquiries: **Kim Newman**

knewman@chipscalereview.com

Copyright © 2013 Haley Publishing Inc.

Chip Scale Review (ISSN 1526-1344) is a registered trademark of Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry. Subscriptions outside of the U.S. (6 issues) by airmail are \$100 per year to Canada or \$115 per year to other countries. In the U.S. subscriptions by first class mail are \$95 per year.

Chip Scale Review, (ISSN 1526-1344), is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December. Periodical postage paid at Los Angeles, Calif., and additional offices.

POSTMASTER: Send address changes to *Chip Scale Review* magazine, P.O. Box 9522, San Jose, CA 95157-0522

Printed in the United States

### FROM THE PUBLISHER

## Of the Industry, By the Industry, & For the Industry

appy New Year to all! As we closed out 2012 with a U.S. presidential election and having avoided sailing over the fiscal cliff and yet surviving the end of times per the Mayan Calendar, we speculate what the New Year has in store. What I see and hear from economic forecasters and industry experts reflect the standard debate between the optimistic and pessimistic perspectives that were consistent with the prognostications of last year and indeed every year!

All industrial sectors will be looking to take advantage of interest rates by making capital investments in new equipment and facilities, as well as looking for strategic acquisitions and joint development opportunities and initiatives including 22nm and 450mm technologies. These were evidenced recently by Intel, Samsung and Taiwan Semiconductor's significant equity investments that range in the billions of Euros ( $\in$ ) with ASML for development of next-generation lithography systems and technologies that will be suitable for patterning 450 mm silicon wafers. The downstream effect will result with supply chains requiring adaptations to accommodate demands. Companies will increasingly make investments in additional technical staff, support and senior management hires.

At the start of the New Year, CSR announced a new Chair of the magazine's Editorial Advisory Board, Dr. Andy C. Mackie, Senior Product Manager at Indium Corporation. Andy sees 2013 as the year when large-scale implementation of 2.5D into the two main driving applications (mobile devices and lower-power servers) will occur with 3D (memory plus logic) finally also emerging in a prototype form. His company, like many, continues expansion into the Asia-Pacific markets with semiconductor and advanced assembly materials, especially in fluxes and similar materials for flip-chip and 2.5D/3D manufacturing and assembly and several offerings into the high-temperature lead-free power semiconductor market space.

With a new editorial board of advisors and a commitment to editorial excellence, I asked the staff at CSR "What does it take to continue CSR's excellence?" The unequivocal answer remains, tons of PhDs, scientists, engineers and technologists from many disciplines that contribute insightful research articles and the continuing support of our subscribers and advertisers. I completely agree!

This edition of CSR is packed with terrific articles by our industry's top authors. We cover BVA PoP, MEMS process solutions, Plasma FIB circuit modifications, cost efficient WLP stacking, WLP functional testing and HVM of 3D, IC packaging economic trends and the obvious requirements of burn-in & test sockets. It is a cover to cover read.

CSR is firmly in the positive-outlook camp for 2013. Jeanne Beacham of Delphon Industries concludes with a great outlook as well: "I am a true optimist and believe that despite today's economic uncertainty, there are plenty of opportunities for growth."

So as an industry, let's spend 2013 investing in the future. We're still here and you, our readers deserve nothing less than the best of the industry, by the industry and for the industry.

Kim Newman

Publisher

"Panasonic equipment delivers best-in-class accuracy and PanaCIM" drives operational efficiency"

"Panasonic equipment delivers the best-in-class accuracy, repeatability, and dependability needed to manufacture the high-quality products our customers expect.

PanaCIM software drives operational efficiency throughout our high-mix, low-to-medium-volume process—from quick changeovers to real-time production monitoring and reduced rework.

Selecting Panasonic has helped us to keep overall manufacturing costs down, maintain our competitiveness, and allow us to pass cost savings to our customers."

Dave Spehar

Director of Operations

As a manufacturer, Panasonic understands the evolving demands of today's electronics assembly manufacturing environment. And that uniquely enables us to provide scalable, integrated, and efficient solutions that help our customers remain viable in a competitive market.

No matter if you're high mix/low volume, low mix/high volume, or anything in between, Panasonic equipment, MES software, and other services can help improve throughput and efficiency while keeping quality reliably high.

Add value, add sustainability, add Panasonic.

For more information, visit www.panasonicfa.com/pennatronics

## MARKET TRENDS

# Global Economy Drives the IC Industry's Cycle

By Bill McClean [IC Insights, Inc.]

hroughout 2012, the expectations for global economic growth consistently deteriorated. Global GDP is estimated to have expanded by only 2.6% in 2012. It should be noted that 2.5% or less worldwide GDP growth is typically considered a global recession (annualized 3Q12 worldwide GDP growth was only 2.5%, equal to the global recession threshold figure). Moreover, IC Insights' forecast for 2013 worldwide GDP growth is 3.2%. Although this figure is higher than the 2.6% growth rate of 2012, it would still be 0.3 points below the 3.5% long-term average.

One of the primary reasons for weak 2012 worldwide GDP growth was the negative GDP growth registered by the Eurozone and U.K. economies. Moreover, the Eurozone is not expected to display a strong rebound, with 0.0% GDP growth forecast for the Eurozone economy in 2013.

China's GDP growth is estimated to have dropped to only 7.7% in 2012 with a modest rebound to 8.1% growth forecast for 2013. While many developed countries would welcome 7% or higher GDP growth rates, for China, this figure is significantly below the 10% and greater annual GDP increases logged from 2002-2009. In an attempt to address its economic "slowdown," the Chinese government was quick to inject stimulus into its economy starting in the second half of 2012 by aggressively lowering interest rates as well as enacting \$156 billion in construction project programs. While this stimulus was too late to have had a significant positive affect on its 2012 GDP growth, China's GDP is likely to get at least a modest boost from this stimulus activity in 2013.

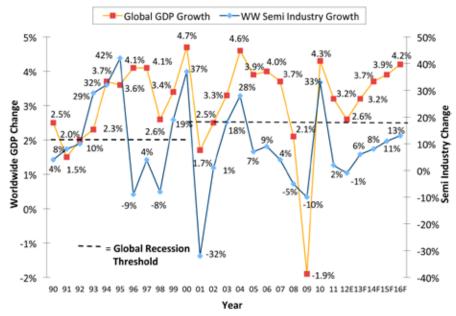

While the correlation between worldwide GDP growth and IC industry growth has historically been good (not great), IC Insights believes that the correlation in 2013 will be very good, as it was in 2012. Using a worldwide GDP forecast of 3.2%, the most likely range for IC market growth in 2013 is 3-7%.

Including the U.S. presidential election year of 2012, over the past 11 U.S. election years since 1972, worldwide GDP growth averaged 3.9%, while semiconductor industry growth averaged 22%. Moreover, the semiconductor industry grew 10% or better in 8 of the past 11 U.S. election years. The three election years when the semiconductor industry did not grow 10% or better (1996, 2008, and 2012), it registered single-digit declines (with a 1% decline occurring in 2012).

The election-year cycle is one reason why IC Insights has identified 2013 as a possible "slow" year in the worldwide economy and semiconductor industry. Over the past 10 post-U.S.-election years, worldwide GDP growth averaged a below-average 3.1% with worldwide semiconductor industry growth averaging only 4%. Moreover, worldwide semiconductor industry growth exceeded 8% in only three of these 10 post-election years (1973, 1977, and 1993), and only once since the late 1970s.

Oftentimes the "problem" with post-U.S.-election years is that many of the subsidies and stimulus measures enacted during an election year are withdrawn or allowed to expire after the election is over. In the case of the U.S., there is likely to be continuing debate and consternation in Congress over whether to keep the payroll tax cuts (unlikely to be extended) and how much to raise existing tax levels in 2013. Although the exact outcome regarding the future U.S. tax structure and budget is unclear, the large amount of uncertainty created by these issues is expected to be a "headwind" on economic growth in 2013. Because of this, the U.S. economy is forecast to show only a modest rebound in 2013 before picking up momentum in 2014.

As mentioned earlier, the correlation between global economic growth and semiconductor industry growth has been relatively good (see **Figure**). In some cases, when the semiconductor market and worldwide economy are moving in opposite directions, the semiconductor industry is usually encountering an inventory "burn" (e.g., 1985), significant overcapacity (e.g., 1996 and 1997), or significant under-capacity (e.g., 1993).

IC Insights believes that the semiconductor industry cycles are becoming increasingly tied to the health of the worldwide economy. While poor semiconductor industry growth has occurred during periods of strong worldwide economic growth, primarily due to semiconductor industry overcapacity and the resulting IC price declines, it is rare to have strong semiconductor industry growth without at least a "good" worldwide economy to support it. Thus, through the forecast period of 2016, annual global semiconductor market growth rates are expected to closely mirror the performance of worldwide GDP growth.

We Bring Possibilities

Need Compliant Grounding for small packages of 2x2 and above?\*

We have the solution.

HCI [Patent Pending]

Bell Contact [Patent Pending]

Need Short Wiping of 0.1mm for your wettable/dimple pad?\*

We have the solution.

Explore these new exciting and outstanding solutions on our website or with our nearest sales channel partner today.

Find out more at:

http://www.jftech.com.my World class company in semiconductor industry

Or e-mail us at: sales@iftech.com.my

Need Fine Pitching Solution of 0.3mm and above?\*

We have the solution.

#### Copyright@ 2013

JF Microtechnology Sdn. Blnd.

[A subsidiary of JF Technology Berhad]

All right reserved. No part of the document may be reproduced or treasunited in any form or by any means, electronic or mechanical, including photocopy, recording or any information storage and retrieval system without permission in writing from JF Microtechnology Sdn. Blnd.

\*For leaded & leadless packages [QFP/QFN/DFN/etc.]

0.3mm

Figure. 1990-2016 Semiconductor Industry Growth vs. Worldwide GDP Growth. SOURCE: IC Insights

### IC Packaging Trends

Total IC unit shipments enjoyed seven consecutive years of growth (2002-2008) before they dropped 7% in the recession year of 2009. Units then rebounded with 29% growth in 2010 and another 2% growth in 2011. IC unit shipments were flat in 2012 but are forecast to display average annual growth of 5% from 2011 to 2016.

IC packaging has evolved from the "old" DIPs (dual in-line packages) to a variety of packages ranging from ultrathin SO (small-outline) packages and CSPs (chip-scale packages) for low-pin-count applications to BGAs (ball grid arrays) and MCPs (multi-chip packages) with thousands of solder ball (or bump) connections.

It is within the newest package categories that the real diversity starts to show. For example, there are BGA designs to meet nearly any packaging need. BGAs can be plastic, tape, or ceramic, wire bonded or flip-chipped, cavity-up or cavity-down, overmolded or encapsulated, single-chip or multi-chip. They can have lead counts ranging from less than 100 to thousands. They may be made very small and thin for portable electronics, or thermally and electrically

enhanced for high-speed systems.

The options for mounting multiple chips in a single package solution have become very diverse. Dice can be placed side-by-side in MCM- or BGA-type packages, numerous dice can be stacked on top of each other in packages the same size as single-chip packages, packages can be stacked atop other packages, bare dice can be bonded together to create a 3D integrated circuit. Additionally, some combination of any or all these technologies can be used to meet the space requirements

and/or performance needs of each particular system application.

Shown in the Table is IC Insights' IC unit shipment forecast by package type, which has been updated to reflect the latest expectations for unit growth over the next several years. Advanced packages such as bare die and waferlevel devices continue to grab market share from older package types, but the mainstay of package types-SO and FP/CC-type packages—were the most widely used in 2012 and are expected to be the most popular throughout the forecast period. Low-lead-count SO packages are used primarily in the packaging of analog and standard logic ICs but can also be found in most other IC categories.

For larger chips, with lead counts that exceed the capability of SOs, LCCs (leaded chip carriers) and OFPs (quad flat packages) are the most widely used package types. Like the SOs, these peripherally leaded packages can be found in just about every IC category. However, the lead counts of LCCs and QFPs are limited to a maximum of about 80 and 400 pins, respectively. BGA-type packages have displaced QFPs, as well as through-hole mounted PGAs, in most applications. BGAs offer the advantages of the extensive use of existing surface-mount technology infrastructure, high boardlevel assembly yields, superior electrical

#### IC Package Shipment Trends (Billions of Units)

| Package Type    | 10    | 11    | 12E   | 13F   | 14F   | 15F   | 16F   | 11-16<br>CAGR | Examples                                                 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|---------------|----------------------------------------------------------|

| SO              | 65.4  | 62.0  | 62.5  | 64.1  | 67.0  | 70.8  | 76.3  | 4%            | TSOP, SSOP, SOJ, LOC,<br>SOT, SC                         |

| FP/CC           | 44.2  | 44.8  | 45.5  | 48.1  | 51.0  | 54.8  | 59.7  | 6%            | QFP, QFN/MLF, Flatpack, PLCC, LCCC, Cerpack              |

| BGA (incl. MCP) | 32.1  | 34.6  | 37.3  | 40.3  | 43.6  | 47.3  | 51.9  | 8%            | PBGA, FPBGA/μBGA, TBGA, LGA,<br>CGA, SiP, S-CSP, MCM-BGA |

| Bare Die        | 10.1  | 11.5  | 12.9  | 13.6  | 15.0  | 16.7  | 18.8  | 10%           | FCOB, COB, COG, COF, TCP                                 |

| Wafer-Level     | 8.7   | 9.6   | 10.5  | 11.3  | 12.7  | 14.7  | 16.5  | 11%           | Ultra CSP, microSMD,<br>eWLB                             |

| MCM             | 1.1   | 1.1   | 1.3   | 1.3   | 1.4   | 1.6   | 1.8   | 9%            | Multichip Modules                                        |

| Through-Hole    | 7.9   | 7.7   | 7.7   | 7.6   | 7.5   | 7.6   | 8.0   | 1%            | PDIP, CERDIP, ZIP/SIP, TO, PGA                           |

| Total           | 169.6 | 171.3 | 177.6 | 186.3 | 198.4 | 213.5 | 232.9 | 6%            |                                                          |

Note: CSPs are included but not considered a distinct package category.

Table. Package Shipment Trends (Billions of Units). SOURCE: IC Insights

### **EXPANDING OUR TERRITORY**

We're excited to celebrate this Lunar New Year with the launch of our new office in Singapore, serving clients in SE Asia, Taiwan and China.

### **ABOUT PLASTRONICS**

Plastronics offers complete, reliable burn-in test socket solutions for the latest packaged devices. We are committed to meeting the challenges of our clients today...and tomorrow.

## **Reliable Sockets and High Performance Pins**

PLASTRONICS GLOBAL HEADQUARTERS 2601 Texas Drive Irving, Texas 75062 PHONE 972-258-2580 FAX 972-258-6771 sales@plastronics.com

PLASTRONICS ASIA PTE LTD 33 Ubi Avenue 3, # 05-22 The Vertex Singapore 408868 PHONE +65 6570 6882 FAX +65 6570 6880 asia@plastronics.com

www.plastronics.com

performance, and higher I/O capability.

Over the next five years, some of the IC packages that will enjoy the strongest growth in demand will be standard and fine-pitch BGAs, multi-chip packages like stacked CSPs, package-on-package assemblies, quad flat no-lead (QFN) packages such as bumped chip carriers

or micro-lead frame devices, and wafer-level packages (WLPs). Three-dimensional ICs built using through-silicon via (TSV) technology are all the rage in the news, but 3D ICs will likely remain a niche technology until after 2013 because there are still several challenges to overcome with this

relatively new technology including thermal management issues and test access for individual wafer/die.

The group of packages that are considered "advanced," including BGAs, CSPs, WLPs, and flip-chip-onboard (FCOB) solutions, represented about 40% of total IC package shipments in 2012. That share is expected to grow to 43% by 2016.

Overall, there are a multitude of IC packages currently in use or under development. The wide variety of packages is driven by the fact that system manufacturers increasingly want personalized packages at commodity prices. These are packages with an optimal balance of thermal and electrical performance, real estate constraint, and low cost, mixed and matched to meet the needs of each particular system application—all in standard outlines or at least built with standard processes.

The integrated circuit industry will continue to enable more powerful machines at lower prices and the packaging industry will play an increasingly important role in making it happen. Developments in wafer-level packaging, system-in-package, and the imminent 3D revolution will enable scaling advances in packaging through 2016. To date, the packaging industry has done a good job of overcoming technology hurdles, but more challenges are in store. Fortunately, global cooperation has so far been good and roadmaps are fairly well-aligned that help address demands for new package architectures, new materials, new processes, and new equipment. All of these will be needed as IC manufacturers begin to move their manufacturing processes to 14nm and smaller line widths.

### Biography

Bill McClean received his BS in business administration and an Associate Degree in aviation from the U. of Illinois; he is President of IC Insights, Inc.; email info@icinsights.com

## GUEST EDITORIAL

## Requirements: Aren't They Obvious?

By David Barnum [Sensata Technologies]

ur business is very exciting because we actually turn raw materials into finished goods that are validating building blocks to other higher level electronic systems that improve and touch our lives in so many ways, every day. The business of designing a burn-in socket, constructing it, delivering it on time, and at a value that meets the customer's expectation, is in itself, a significant accomplishment requiring a lot of information, with no one application exactly the same as another.

Burn-in sockets are subject to thermal and electrical stress, in a controlled environment, for the purposes of inducing the failure of "marginal" semiconductor devices, or those that have inherent defects resulting from manufacturing excursions that cause time- and stress-dependent failures. Translation: burn-in sockets try to induce a failure to prevent marginal semiconductor devices from getting into mission critical, or high-value systems.

Burn-in sockets have a number of sensitivities associated with them. Because we are trying to force failures, they are presented with many types of temperature, humidity and duration profiles, and many types of manual, automatic, and semi-automatic operations are used to present the chip to the burn-in sockets, which are usually mounted on a multi-site burn-in board. In addition, there are many types of chambers and stacking geometries that come into play to process all of the devices needed to be burned-in, in a timely manner.

If we start to list the number of

considerations, given the dimensions of the challenge, the list of items is comprehensive, but crucial in attaining the goal of getting the right product for the right customer application. As engineers, we usually leverage our background and make many assumptions that sometimes lead to a win, but sometimes miss the mark considerably. To better approach the challenge, a list of requirements along with the particular package drawings are keys to presenting a winning solution. Listed below are descriptions of some of the more critical requirements and key factors enabling winning burn-in socket designs.

- 1. Mechanical outline of the package (including final thickness) with the pad or ball dimensions, and the package's material composition. As long as the package mechanicals stay stable throughout the development there are usually minimal issues here. If the package thickness or material composition changes between initial definition and final state, then real issues will occur to the point where the socket will not work initially.

- 2. Burn-in equipment's or burn-in test condition's electrical requirements: resistance, capacitance, inductance, power requirements. Usually, these are well defined, but sometimes there are discrepancies in power per pin requirements, which again challenge the socket's ability to perform in the burn-in protocol.

- 3. Burn-in test condition's cycling dwell times and profile: how long and at what intervals do the parts see heat, cold and get tested electrically. This issue has come-up many times

as users try to induce failure in their devices. Thermal creep and set of both plastic and contacts can occur, dependent on dwell times at elevated temperatures for both the device and the socket, which can lead to catastrophic failures.

- 4. Applied loading and unloading/ packaging equipment mechanicals. This is sometimes a huge issue in high pin count devices (>350 contacts) and in production environments where handling can shorten socket life substantially. The termination load of the socket cover can limit the amount of sockets used per board or loading fixture, or an individual operator's ability to load the socket. The physical handling of the board from loading fixture to oven and back to packaging has a substantial effect on the sockets near the edges of the burn-in board, as many times we see broken parts from handling issues.

- 5. Height of contacts off board, the termination datum, board-to-board spacing, and socket density on the burn-in board. In a production environment, these are requirements, as they determine how much mechanical stress the sockets and corresponding equipment will see, which will determine how long both sides of the system will endure.

- 6. Operating temperature requirements. These requirements include those for the device under test, and those mechanical (board-to-board or rack spacing) and electrical constraints of the system (power availability beyond the basic controller), relative to the use (or not) of a passive heat sink, active heat sink, chamber

control, or local control. Some socket companies can add value in the design of the complete system, which, if defined in the beginning, can lead to a very robust and flexible system for future requirements.

7. Cycling: a practical amount of durability cycles are needed. Users want the maximum available for "design

security;" however, many times the requirements are well above the life of the particular device being burned-in.

Most of the time the first and second items listed above are provided, which gets us to first base. However, what is critical in the success of the program is an understanding of the remaining items in the overall execution of a robust and

value-oriented design. Socket OEMs certainly understand that many times users want to "stack" the requirements and use certain "production" level sockets, which have been optimized for one set of conditions with many other conditions for which they were not intended. Unfortunately, this usually ends-up with a call into the OEM describing failures. Other times, the design of a new socket misses the mark because Items 3-7 were not fully comprehended, or communicated upfront, which is usually a shared responsibility between parties. Item 7 is always an interesting subject to discuss, as cost via contact design is a huge determining parameter regarding the practical amount of cycles required. The real key is how the parts are used in a production environment.

In summary, requirements for robust and value oriented burn-in socket designs are dependent on a whole host of requirements that are sometimes not given enough time to be thoroughly understood, as many times the socket OEMs are brought in towards the end of the chip development cycle. As can be seen from the list above, there are many things to comprehend when designing a burn-in socket. While for the most part, the industry does a good job on both sides of the equation, we do experience enough "hiccups" to inspire the holistic set of requirements such as those presented above to ensure successful execution in any burn-in application. In this business, there are a plethora of packages that can house die. It is incumbent on all of us to work together to better define requirements upfront to produce better outcomes for both the supplier and the user of burn-in sockets.

### **Biography**

David Barnum received his BS degree in mechanical engineering from the U. of Massachusetts-Lowell, and studied finance, operations management and marketing at the U. of New Haven. He is senior director and global business unit manager at Sensata Technologies; email dbarnum@sensata.com

The NexJet® System\* featuring the one-piece Genius™ Jet Cartridge\*

The Genius Jet Cartridge is the only system part that contains fluid — the

only piece that needs to be changed and cleaned. It is easily removed in seconds without tools.

Built-in memory tracks and stores usage data, thereby increasing quality and consistency in pre-

cision manufacturing applications such as adhesive dispensing, precise coating and underfill.

See Nordson ASYMTEK at SEMICON China, Booth #3663

You can rely on our award-winning support network. Visit our website to contact your local office:

\* PATENTS PENDING

USA | China | Europe | Japan | Korea | India | Singapore | Taiwan

Find out more now: advancedjetting.com

## **GUEST EDITORIAL**

## Robust Process Solutions for MEMS Flip-Chip Applications With Medium Density Lead-Free Solder Interconnects

By Dave DiPaola [DiPaola Consulting]

ith the proliferation of MEMS in sensor products in a variety of applications, packaging challenges continue to be at the forefront of successful production launches. Furthermore, package shrinkage, cost pressure and rapid time to market magnify these challenges because traditional approaches can no longer meet these constraints. The four major packaging challenges that consistently appear in product development are electrical interconnection, mitigating the effect of packaging strains on sense element performance, protecting the sensor from the environment, and proper management of temperature distribution and resulting material behavior. Given the complexity of these topics, this article will review the challenges in electrical interconnection for increasingly smaller MEMS flip-chip applications using lead-free solder for medium density I/O, size sensitive medical applications. With bump sizes of 90µm and bump pitch of 150µm, particular attention in component handling, material selection and process development were required to overcome challenges of poor reflow due to oxidation and shorting, while minimizing tooling and process cost. In particular, cleanliness, material handling, flux selection and application, metallization and reflow profile tuning are reviewed in detail for a robust design.

### Challenges of Lead-free Solder Interconnects

There are several factors that increase the difficulty of lead-free solder interconnects with medium density I/O for MEMS flip-chip applications. These factors include high reflow temperature, increased surface area of the bump relative to its volume, flux and cleaning limitations, necessity for underfill and tight I/O spacing. In the transition from Sn-Pb solder to those containing solely tin, tin, copper and silver, or other variants, the metal or alloy melting temperature increased requiring higher reflow temperatures to ensure proper wetting of the joint. This higher temperature causes oxidation to develop more quickly on metallization and solder making it more difficult to obtain a properly wetted bump. This problem becomes even more challenging as bump size decreases and the bump's external surface where oxide is present becomes a larger percent of the total solder volume. Therefore, the ratio of oxidized to non-oxidized solder increases and increased heat is needed to overcome this effect creating an undesirable cycle that cannot be sustained. Flux is used to prevent oxide growth and remove it from the bumps' external surface during reflow. However, aggressive fluxes cannot be used because of their corrosive nature, ionic contamination and inability to be cleaned post reflow. The fragile nature of MEMS devices for medical

applications and the narrow gap between chip and substrate make cleaning post reflow ineffective or not practical due to product damage. Underfill is also a requirement in this application to prevent shorts from tin whiskers between bumps and to minimize stress on the bumps from temperature fluctuations for medical products located outside of the body. The tight I/O spacing also results in a smaller process window to prevent solder shorting. Despite these challenges, there are a number of combined steps that can be taken to create robust leadfree interconnects.

#### **Process Considerations**

Product cleanliness and material handling are crucial but often overlooked steps in creating a robust solder joint. Rigid and flexible printed circuit boards readily absorb moisture and this moisture is outgassed from the product during reflow thereby increasing oxide growth on the bump. To prevent this, circuit boards can be pre-baked at 125°C for 2-6 hours (depending on environmental exposure and moisture present) in an oven to drive off moisture prior to reflow. In addition, metallization on the substrates should be selected to minimize oxidation growth during this step. If the substrate is bumped rather than the MEMS flip-chip, another option is to ship the products in vacuum sealed, desiccant bags and store them in nitrogen back-filled

chambers when not being processed to limit exposure to humidity and oxygen. Product cleanliness is equally important because specific contaminations such as sodium chloride can accelerate oxidation growth and ionic contamination can create shorts in the presence of moisture. Clean process environments and aqueous-based cleaners followed by post bake are often effective.

The cleaning action of flux to remove oxide is another critical step to a proper solder reflow process. Without the post reflow cleaning option for many medical MEMS devices, rosin-based ROL0 fluxes without halides that completely evaporate during reflow are recommended for use. The use of halides in fluxes provide better cleaning action but are avoided because of their corrosive nature and they cause ionic contamination that can lead to shorts without cleaning. One flux option that provides more aggressive cleaning but contains no halides is ROM0. It is best to limit flux application to the lower half of the bump covering 30-50% of its surface. In some cases, more flux is required to clean the oxide present and maintain activity during higher temperature processing of lead-free solders. In either case, it is important to ensure no residue is left that may interfere with the underfill process creating voids or adhesion issues. Lastly, it is important to choose a flux with an 8+ hour working life and that has sufficient tackiness to prevent the part from skewing during reflow. MEMS devices are extremely light weight and can be easily moved from the desired position.

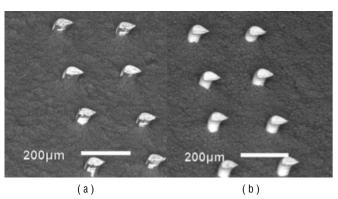

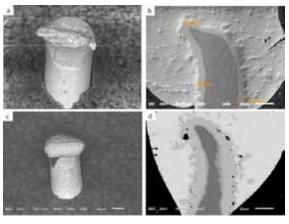

Solder reflow profile selection and substrate metallization are of equal importance to the previous steps in achieving proper bump wetting and collapse. In an ideal scenario, it is desired to achieve a 15-30% collapse of the solder bump and have the solder completely wet the substrate surface. Examples of properly wet and non-wet bumps are provided in Figure 1.

A typical reflow profile for SAC 305

Figure 1. Non-wet and wet solder bumps.

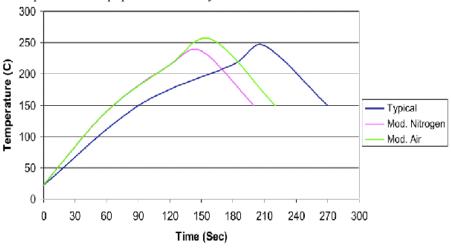

lead-free solder consists of pre-heating including soak, reflow and cool down zones. To achieve the proper wetting defined above for MEMS applications, the typical reflow profile needs to be adjusted. More specifically, it is important to minimize the preheat zone to keep the flux active and prevent it from drying out. This could result in nearly a straight ramp to the reflow zone. In addition, the reflow zone needs to be adjusted to compensate for the level of oxide on the bumps and type of solder being used. It's best to keep reflow peak temperature as low as possible while still maintaining a reasonable process window. If the reflow is performed in a nitrogen atmosphere, which is highly recommended to limit oxide growth, the peak temperature will be lower and the reflow zone shorter. If reflow is performed in air, one can expect higher reflow peak temperature for longer duration. Although a nitrogen atmosphere is recommended, it is not always easily implemented, especially when production equipment is already in place, or funds are extremely limited in a medical device startup. In other cases, the product may already be launched with an air reflow process with poor yield, and it could be weeks before an equipment upgrade to add nitrogen can occur. Figure 2 shows a typical lead-free solder reflow profile with two modified versions, for air and nitrogen, as described above.

After reflow is complete, underfill application is an important step to minimize the stress induced in the solder joints from differing coefficients of thermal expansion (CTE) of the substrate and MEMS flip-chip. The underfill minimizes shear forces on the bump and causes the substrate and chip to slightly bend as one unit. Another critical function of the underfill is to prevent tin whiskers from creating shorts between the bumps. Leadfree solders have a high percentage of tin and are highly susceptible to this unpredictable failure mode. NASA has observed whisker formation after a few hours, and in some cases, they do not form for many years [1].

A robust metallization for the bond pad on the mating substrate is also required to prevent oxide growth, ensure proper wetting and excellent adhesion. On printed circuit boards, this metallization is often electrolytic or electroless nickel with flash gold over a copper base layer. There are multiple

Figure 2. Typical and modified lead-free solder reflow profiles for SAC 305.

## And now, the perfect name

Qi-nex [kuh-nekts] 1. Over 40 years of reliable burn-in and custom connections; 2. Quality interconnects for nex-gen solutions.

Introducing Qinex, the new brand name for superior interconnection solutions from Sensata Technologies. Qinex, the new word in perfect pitch.

**QUALITY.** High-value interconnection solutions since 1970.

- 24/7 global engineering

- 24/7 global support teams

- Local engineering and sales

- Six Sigma quality management

- Proven, reliable high-volume manufacturing

- Expert molding, design, and customization

PARTNERSHIP. In a fierce global market, only Qinex reliably supports the innovation, reputation and competitiveness of your business. We'll work with you to get it right, the first time.

INNOVATION. More I/O choices, smaller form factors, superior performance in less time.

- Latest 3D design tools

- On-site model shops

- Rapid prototyping

- Advanced thermal analysis

- · Design on demand

- Broad range of innovative contact designs

40+ years of perfect pitch. And now, the perfect name.

WEB www.qinex.com

EMAIL qinex@sensata.com

CALL 1-508-236-1306

options for the chip metallization, but one popular example is immersion gold over electroless nickel with a zincated aluminum base layer. Both Pac Tech and Uyemura have reported differing levels of success with palladium as a diffusion barrier between the nickel and solder. The tin and nickel intermetallic is brittle and can be a source of failure

in high stress conditions such as drop test. There are examples of palladium use between the nickel and gold layers, or as the top layer without gold [2-3].

### **Summary**

The difficulties in creating robust lead-free solder joints for medical MEMS flip-chip applications

of increasing smaller size with confounding process parameters and materials is a real challenge. The solution to this problem lies within an intertwined mix of oxide growth minimization, proper material selection and application, and subtle process parameter adjustments. More specifically, cleanliness, proper storage and handling or pre-bake, flux and its application, the solder reflow profile, chip and substrate metallizations and underfill, are all critical elements in the process. Hence, when each of these parameters and materials are designed to work together, robust lead-free solder joints with high first-pass yields can be achieved 9

#### References

- 1. J. Brusse, H. Leidecker, L. Panashchenko, "Metal Whiskers, A Discussion of Risks and Mitigation," Proc. of Symposium on Part Reprocessing. NASA, 12 Nov. 2008; Web, 12 Feb. 2012, <a href="http://nepp.nasa.gov/whisker">http://nepp.nasa.gov/whisker</a>.

- 2. G. Milad, D. Gudeczauskas, "Solder Joint Reliability of Gold Surface Finishes (ENIG, ENEPIG and DIG) for PWB Assembled with Lead Free SAC Alloy," Solder Joint Reliability; Uyemura International Corp. 2012; Web. 14 Nov. 2012; http://www.uyemura.com/solder\_joint\_reliability.htm#5

- 3. T. Teutsch, "ENIG vs. ENEP(G) Under Bump Metallization for Lead-free WL-CSP Solder Bumps a Comparison of Intermetallic Properties Using High Speed Pull Test," IMAPS International Conf. on Device Packaging. 17-20 March 2008, Scottsdale, AZ. Pac Tech; Web. 14 Nov 2012, http://pactech.com/files/56%20NiPdAuforIMAPS%20 Scottsdale%202008.pdf

### **Biography**

David DiPaola is Managing Director for DiPaola Consulting, www.dceams.com; email david@dceams.com

## INDUSTRY NEWS

### Ultratech Acquires Assets of Cambridge Nanotech, Inc.

Ultratech, Inc. has acquired the assets of Cambridge Nanotech, Inc. Based in Cambridge, Mass., Cambridge was a leader in atomic layer deposition (ALD) solutions with hundreds of system installations in research and manufacturing settings worldwide. Financial terms of the transaction were not disclosed. With this acquisition, Ultratech expands its nanotechnology and intellectual property (IP) portfolio with ALD technology to provide solutions for new layers within the electronics industry and entry into new markets, such as biomedical and energy.

The company noted that ALD technology will be in high demand in volume manufacturing environments, and in particular for micro-electromechanical systems (MEMS), implantable devices in the biomedical sector, and batteries and fuel cells in the energy arena. ALD is an enabling technology and provides coatings and material features with significant advantages to other existing techniques.

Ultratech Chairman and Chief Executive Officer Arthur W. Zafiropoulo stated, "As a global leader in experimental ALD solutions, Cambridge has developed a portfolio of valuable technology and systems. We plan to integrate the intellectual property acquired from Cambridge Nanotech into Ultratech and include the ALD systems in our nanotechnology product group. By increasing our IP and expanding our nanotechnology portfolio to new levels, we expect to generate a new revenue stream in existing and new markets."

### A\*STAR's IME Launches 2.5D Silicon Interposer Multi-project Wafer Offering

The Institute of Microelectronics (IME), a research institute of the Agency for Science, Technology and Research (A\*STAR) in Singapore, announced the launch of its 2.5D through-silicon-

interposer (TSI) multi-project wafer (MPW) service, aimed at providing a cost-effective platform to do research and development prototyping and proof-of-concept in 2.5D TSI technology.

Supported by IME's state-of-the-art 3D through-silicon-via (TSV) engineering line, the MPW service is a one-stop solution for 2.5D TSI R&D prototyping that comes with comprehensive design kits, via and redistribution/bumping technology, as well as packaging and assembly capabilities. By enabling the heterogeneous integration of different functionalities including logic, memory, analog/RF, photonics, microelectromechanical systems, devices with more functionality, smaller form factor and less power consumption can now be realized.

The service will enable the academic, research and industrial community to

develop 2.5D research test vehicles with leading-edge designs, materials and processes so that they can be applied to products such as smart phones, tablets, networking and sensors, and biomedical applications.

## A\*STAR's IME to Collaborate with SFC Fluidics® on Automated Biosensor

A\*STAR recently announced that through its Institute of Microelectronics (IME), it will be collaborating with SFC Fluidics<sup>®</sup>, a USA microfluidics-based biomedical device development company, to develop a portable diagnostic tool for rapid triaging of traumatic brain injury (TBI) victims and to improve the treatment strategies. TBI is one of the most common causes of death and disability in the world, usually resulting from blasts, falls,

knocks, traffic accidents, and assaults.

The proposed diagnostic tool is a fully-integrated, automated biosensor device that requires only a drop of blood to detect up to three biomarkers released by the brain after sustaining injury. The biomarker readings will be displayed on an easy-to-read screen, along with an indicator, alerting the caregiver to the severity of the injury.

Unlike conventional diagnostic tools such as neurological tests and computed tomography (CT) scans, the biosensor device does not require any trained personnel for sample handling. The portable feature of the device facilitates rapid on-site diagnosis of the injury. Caregivers will be able to respond quickly with the proper course of treatment to prevent injury aggravation.

The biosensor device leverages and integrates IME's silicon-based microfluidic sensor and biosensor technology and bio-electrochemical assay development capability. IME has built up strong capabilities in biomedical microsystems and has established deep collaborations with the clinical community and key industry partners in Singapore to advance silicon-based point-of-care diagnostics devices.

SFC noted that, by leveraging IME's industry standard mass production facilities, the company will be able to cut down the product development cycle time. SFC's VP of R&D, Sai Kumar, stated that the TBI project is the start of a longer term collaboration that the company will explore together with IME.

### AG Semiconductor Services Enters Remarketing Business

AG Semiconductor Services, LLC (AGSS), announced the formation of a new remarketing services division targeting 150, 200 and 300mm semiconductor, IC test/assembly and printed circuit assembly equipment. The company has made a significant investment in personnel and business systems to ensure its ability to deliver a full slate of remarketing services in

addition to the purchase and sale of surplus semiconductor manufacturing equipment, turnkey solutions, inventory management, market metrics, compliance control, and the ability to reach the largest number of buyers. A seasoned team has been brought on board to ramp up the remarketing activities. The majority of the new remarketing team came to the company from the former GE Capital Global Electronics Services' (GES) remarketing business.

### ZESTRON Opens Japan Headquarters and Technical Center

ZESTRON has opened its Japan Headquarters and 6th Technical Center located in Kanagawa; it represents the company's 4th Asian Technical Center.

**Figure**: ZESTRON Japan Headquarters and Technical Center

The investment enables the company to introduce leading edge aqueous-based cleaning agents within this market as an environmentally sound alternative to the many solvent-based cleaning products currently used.

Mr. Daido Sawairi, General Manager for ZESTRON Japan, is responsible for operations and leading the local application engineers and sales team. He has over 20 years of domestic and international business experience in the electronics field and has held various management positions during his career.

### Test Advantage Hardware Names Billy Liu Country Manager for Taiwan

Boston Semi Equipment LLC (BSE

Group) announced the appointment of Billy Liu as Test Advantage Hardware's country manager for Taiwan. Liu is responsible for managing Test

Billy Liu

Advantage's expanding business for new and pre-owned semiconductor test equipment, spare parts, technical capabilities and financial solutions within Taiwan.

Liu will work within the company's newly formed Taiwan operation, Test Advantage PTE Ltd., Taiwan Branch, with additional responsibilities for staffing and recruitment. He brings a background in semiconductor test and over 18 years of experience in the technology industry within Taiwan.

### Philippe Wieczorek Named Minalogic's Software Director

Minalogic announced that Philippe

Wieczorek has been named director of the Software Department. He will be responsible for coordinating and expanding

Philippe Wieczorek Minalogic's software development activities, including projects that help cluster members integrate innovative software features in microelectronics and develop smart miniaturized products and solutions.

Wieczorek most recently served as chief of staff of Hewlett Packard's Internal Sites Management Team (ISMT) in Grenoble. In that position, he focused on creating R&D activity and on ISMT's relationships with institutional players and academics. At HP, Wieczorek also was an innovation manager for the company's Communications and Media Solutions business unit, managing international projects.

Earlier in his career, Wieczorek worked in the network and telecommunication fields, where he held engineering

positions ranging from software development to engineering manager. He also worked for five years at Cap Gemini S.A. He holds an MS in computer science from McGill University in Montreal, Canada, and an engineering degree from INSA Lyon, France.

### Patrick Boisseau, Head of Leti's Nanomed Program, Elected Chairman Of the European Technology Platform on Nanomedicine

CEA-Leti has announced that Patrick Boisseau, the head of Leti's nanomedicine program, has been elected chairman of the European Technology Platform – Nanomedicine (ETPN), a joint initiative between industry, academia, clinicians and the European Commission to help build a profitable nanomedicine sector in Europe.

Patrick Boisseau profitable nanomedicine sector in Europe. Most of the innovation in Europe is occurring in research labs and small to midsize enterprises (SMEs), including start-ups that have spun off from universities and research institutes.

Boisseau said two of his primary goals during his twoyear term as chairman of ETPN are keeping the nanomed innovation that is underway at many European facilities and SMEs in Europe, and to help build a nanomedicine sector that can compete strongly with Asia and the U.S. "One key way to do that is to organize a supply chain of SMEs to facilitate the transfer of innovation and technology to large companies and make these technologies available to patients as soon as possible," said Boisseau. "It also will require us to build key infrastructure in Europe, such as an EU nanotechnology characterization lab or a network of good manufacturing practices sites for medical nanomaterials. This initiative also will be a good opportunity for leading European institutes like KTH, EPFL, Helmholtz Foundation, Tecnalia, Fraunhofer, SINTEF, and Leti to expand their nanomed partnerships with both SMEs and large companies."

Boisseau has chaired the ETPN working group on nanodiagnostics since the ETPN was formed in 2005. In the same election, Dr. Laurent Levy, CEO of Nanobiotix, was elected vice chairman of ETPN. He represents SMEs on the platform's executive board.

### Edward Watkins Joins SMT International as Senior Research Chemist

**Edward Watkins**

SMT International, LLC has just announced the hiring of Edward Watkins as a Senior Research Chemist for the company's AMTECH solder products. An accomplished chemist with decades of experience in research, product development and analytical testing, Mr. Watkins will utilize his extensive

background and experience to assist in the development of innovative solder pastes, fluxes, and process support products utilized in circuits assembly.

Watkins' educational background includes degrees from Susquehanna University (BA) and Pennsylvania State University (PhD), as well as serving as a full-time associate research scientist at Yale University. Watkins' resume also includes working for global corporate leaders such as Pfizer, Dow Chemical and Amgen. These and other experiences have allowed Watkins to take a leadership role in product research and development, intellectual property rights and patents, technical writing, manufacturing and QC process development, regulatory investigations and filings, as well as managing teams of research scientists.

### ESCATEC Promotes Markus Walther to CEO

ESCATEC has announced the appointment of Markus Walther to the role of CEO of the ESCATEC Group, effective January 1, 2013.

Markus Walther January 1, 2013. Markus started at ESCATEC as a Technical Manager 23 years ago and advanced through the company to his current role as COO. The position of COO will remain open until a suitable candidate is selected.

Christophe Albin, Executive Chairman of the Board of Directors and founder of ESCATEC, said, "Markus has made major contributions to the success of ESCATEC, helping the company establish itself as a major global player in the electronics engineering and manufacturing ("E2MS") industry through offering world class customer service backed by Swiss quality and reliability. It is particularly gratifying that our policy of continually investing in our people

and their career development produces outstanding staff such as Markus, who has worked in most departments during his 23 year career at ESCATEC, and therefore has hands on experience to draw upon to bring out the best in people."

Commenting on his appointment, Markus Walther added, "I am very honored to continue to serve ESCATEC in my new appointment as CEO. Handing the day to day operational management of the business to a new COO will enable me to apply more of my time to supporting the strategic growth of the business. We see significant opportunities to grow through more focus on the US market, continuing to expand our presence in Europe, and offering a very effective manufacturing alternative in South East Asia to the ever increasing cost of China. It will also allow me to continue the development of, and investment in, our employees, our manufacturing technologies and capacity in order to support our growth strategy and with customer service always in our minds. We call this ESCATEC's way to success."

### Barry Cox Joins Touchstone Semiconductor as Executive Chairman of the Board

appointed Barry L. Cox Executive Chairman of its Board of Directors. Cox brings more than 45 years of leadership experience in the

Barry Cox experience in the semiconductor industry. He has held senior management positions including President, CEO and Chairman of the Board at several private and public corporations. In addition to Touchstone, he is a member of the Board of Directors of Pixelworks and Audience. He has served on the Board of Directors of 18 corporations and been involved

in four public offerings, two secondary offerings and 11 acquisitions at these companies. He holds a Bachelor of Science degree from the US Air Force Academy and a Master's in Business Administration from Boston University.

### Carsem Expands Role of VP Allan Calamoneri

Carsem announced that Allan Calamoneri has assumed the responsibilities of VP of Sales, North America, effective immediately. Calamoneri is based in the Scotts Valley, California office and reports to Albert Law, Carsem's VP of World Wide Sales and Marketing.

Calamoneri – who has a 23-year career in the semiconductor industry – has COO experience and a track record of successful results in both domestic and international management roles, noted the company. Associated with Carsem Inc. since 2004, his most recent experience was as VP of Test Business Development. In his new, expanded role, Calamoneri will have responsibility for the entire selling organization of Carsem in North America. Reporting to him are three regional sales directors and a technical sales director.

### **ECTC** Registration is Now Open

This year's Electronic Components and Technology Conference (ECTC) will feature more than 300 high-quality papers over 36 oral sessions, four interactive presentation sessions and one student poster session.

The sessions cover peer-reviewed papers on 3D/TSV, embedded devices, LEDs, co-design, RF packaging, electrical and mechanical modeling, advanced packaging and interconnections technologies,

materials, assembly manufacturing, system packaging, optoelectronics, reliability, MEMS, and sensors.

There will also be four invited sessions:

### LED Packaging Technologies and Market Trends – For A Brighter Future

Chair: Ricky Lee – Hong Kong University of Science and Technology

## Packaging Challenges Across the Wireless Market Supply Chain

Chair: Lou Nicholls - Amkor

### The Role of Wafer Foundries in Next Generation Packaging

Chair Sam Karikalan - Broadcom Corporation

### CPMT Seminar: Advanced Low Loss Dielectric Materials for Large Data High-speed Wide Band Transmission

Chair: Kishio Yokouchi – Fujitsu ITL And a special modeling session: Modeling and Simulation Challenges in 3D systems.

Chairs: Yong Liu - Fairchild Semiconductor; Dan Oh - Altera

The ECTC also features 16 CEUapproved professional development courses and over 70 exhibitors.

The 63rd ECTC, sponsored by the CPMT society of IEEE, will be held May 28 - 31, 2013 at the Cosmopolitan Hotel, Las Vegas, Nevada. For more information and registration, visit www.ectc.net.

### Call for Papers International Wafer-Level Packaging Conference

The SMTA and *Chip Scale Review* are pleased to announce plans for

the 10th Annual International Wafer-Level Packaging Conference and Tabletop Exhibition. This premier industry event explores leading-edge design, material, and process technologies being applied to Wafer-Level Packaging applications. There will be special emphasis on the numerous device and end product applications (RF/wireless, sensors, mixed technology, optoelectronics) that demand wafer level packaging solutions for integration, cost, and performance requirements.

The IWLPC Technical Committee would like to invite you to submit an abstract for this program. Abstract deadline is March 29, 2013.

The conference includes three tracks with two days of technical paper presentations covering: Wafer

Level Packaging; 3-D (Stacked) Packaging; and MEMS Packaging. Also we will offer professional development courses.

If you would like to present at this conference, please submit a 200-300 word abstract by March 29th, 2013. Please include a title, author name, and contact information with your abstract.

## Note that technical papers are required and will be due August 23, 2013.

For more information on the conference, please contact Patti Hvidhyld at 952-920-7682 or to patti@smta.org. For information to exhibit and sponsorship opportunities please contact your CSR sales rep or CSR Publisher at info@chipscalereview.com

### **Cost Efficient Wafer-Level Stacking Technologies**

By Mariam Sadaka, [Soitec USA] Ionut Radu, Chrystelle Lagahe-Blanchard, [Soitec France] Lea Di Cioccio [CEA-Leti]

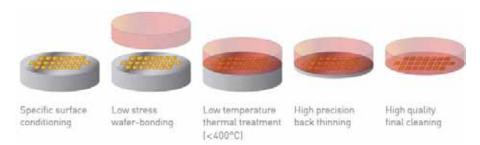

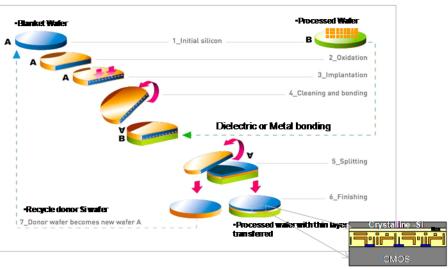

D integration aims at providing highly integrated systems by vertically stacking and connecting various materials, technologies, and functional components together. In this emerging field, new technologies and integration schemes will be necessary to meet the associated manufacturing challenges. To address these challenges, we have developed two wafer-level stacking technologies – Smart Stacking technologies – Smart Stacking and Smart Cut<sup>TM</sup> – for improving the process cost efficiency and providing submicron alignment capability.

### **3D Process Integration Options**

There are a number of 3D process integration options – the vertical stacking of top and bottom layers is one example. This stacking can be performed in two different ways: waferto-wafer (W2W) bonding, or die-to wafer (D2W) bonding. W2W bonding is where the entire top and bottom wafers are bonded together. D2W bonding is where the top layer is diced into chips that are individually stacked using pick-and-place on top of a bottom wafer. The bonding process for the two approaches is collectively performed in a single step. Dicing of the W2W stack is done through the entire bonded stack, whereas dicing for D2W is done through the bottom wafer with the bonded die

With these two stacking options, different trade-offs arise. While D2W stacking uses known good die (KGD) and facilitates the integration of heterogeneous technologies, W2W stacking simplifies the stacking process flow and maximizes the process throughput for homogeneous

Figure 1a: Process schematic of the Smart Stacking technology.

technologies with matching die size. W2W bonding is a fab-compatible process with throughput independent of die size. D2W integration does not offer the same level of cleanliness when using standard wafer processing equipment, and wafer cycle time is directly impacted by die size [1]. W2W bonding is most suitable for applications with high wafer yield and matching die size; one example is memory stacking, which also benefits from a variety of repair strategies [2].

While there are still many remaining issues for 3D integration, cost is certainly a major challenge. We have developed a W2W high throughput direct bonding to improve process cost efficiency and to provide sub-micron alignment capability required for high-density through-silicon vias (TSV) [3]. This article will describe our building blocks for 3D IC wafer-level stacking: Smart Stacking – a high-throughput low temperature direct wafer bonding with sub-micron alignment, and Smart Cut – a low-temperature layer transfer stacking process.

### **Smart Stacking**

Smart Stacking is a W2W stacking technology platform of partially or fully processed wafers (**Figure 1a**). The

process includes surface conditioning, room temperature low stress bonding with alignment, low-temperature postbond anneal, grinding and thinning. Room temperature bonding ensures low thermal expansion mismatch, less stress and mechanical deformation, which are critical for high alignment accuracy [4]. To address the thermal budget constraint imposed by stacking of backend of the line processed wafers (i.e., < 400°C), specific pre-bonding surface conditioning and a post-bonding thermal treatment were developed to control and increase the bonding strength within the reduced thermal budget window. High bonding energies where achieved thereby providing compatibility with aggressive wafer grinding and thinning processes [5, 6].

The low-temperature wafer bonding step includes dielectric bonding or patterned metal bonding. Dielectric bonding provides a mechanical bond and the metal bonding provides a mechanical as well as an electrical bond between the bonded wafers. Smart Stacking with dielectric or metal direct bonding exhibits a similar process throughput of 15-20 wafers/hr unlike other bonding processes, which could take up to 2-4 wafers/hr [7].

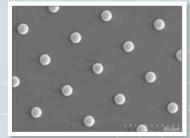

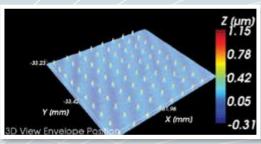

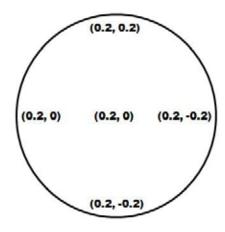

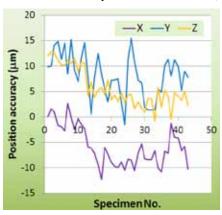

**Figure 1b**: W2W alignment accuracy across a 300mm wafer.

Precision W2W alignment represents a key requirement for the waferlevel vertical integration of 3D ICs. Following the preparation of the patterned surfaces, the processed wafers are bonded using an EVG Smartview® tool. The common alignment specification for this tool is  $\pm 1 \mu m$ , and the alignment is measured using an infrared transmission microscope. Since no external force or pressure, or temperature cycle, is applied during the bonding process, excellent alignment with minimum mechanical deformation is obtained. W2W alignment accuracy of ~0.2µm across 300mm wafers has been achieved (Figure 1b) [5, 6].

#### Oxide-Oxide Direct Bonding

Smart Stacking technology based on low-temperature dielectric, hermetically sealed, and reliable (MIL-STD883) direct bonding, is a promising path for 3D integration that benefits from established oxide-oxide bonding technology [8]. The motivation behind dielectric bonding is to achieve a mechanical bond between the face-to-face (F2F) bonded wafers without introducing new materials in order to maintain manufacturability and reliability standards. This stacking process requires a TSV last approach to form the desired inter-wafer connection.

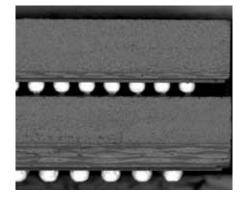

Direct bonding of two oxide surfaces requires considerable control of surface properties. The Smart Stacking technology was demonstrated on 300mm wafers with more than 10

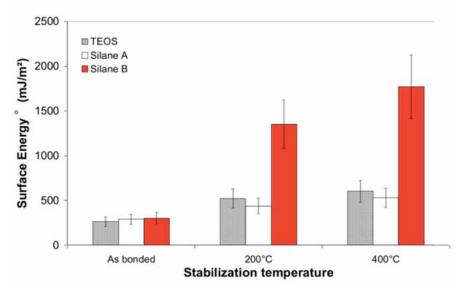

layers of backend metal (10ML) and a deposited oxide layer on top acting as the bonding layer. Wafer topology was controlled by a chemical-mechanical polishing process that maintains wafer edge quality and wafer micro-roughness <0.5nm RMS. This process is fully compatible with common interconnect planarization capabilities [5]. It is demonstrated that with the appropriate choice of oxide and pre-bonding surface

conditioning, high bonding energies can be achieved even after low temperature treatments. Low-temperature deposition of plasma-enhanced chemical vapor deposition (PECVD) silane-based oxides and dry plasma activation achieve surface energies >1J/m² at only 200°C (Figure 2a). An acoustic microscope image of two bonded 300mm wafers with more than 10ML show excellent defectivity at the

Figure 2a: Surface energy ( $\gamma$ ) evolution with temperature of oxide bonding stacks using three different deposited oxides.

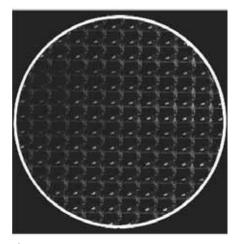

bonding interface and with minimum edge exclusion (Figure 2b) [5].

**Figure 2b**: Acoustic microscope image of the oxide bonding interface of 300mm processed wafers.

#### **Metal-Metal Bonding**

Smart Stacking technology based on low-temperature patterned metal bonding enables the formation of electrical connections during the stacking process—a promising path for high-density 3D interconnects [9]. Even if TSVs are still needed for power, input/output (I/O), and signal routing through the different strata, metal bonding has a significant bandwidth advantage over dielectric bonding [10].

Unlike thermo compression, the non-thermo compression bonding is performed at room temperature under atmospheric pressure and is based on molecular adhesion between surfaces in contact. The bonding process does not require any additional processing steps; standard dual-damascene processes and surface treatment techniques are optimized to ensure smooth hydrophilic surfaces for good bonding conditions [6]. The bonding can be done directly after standard backend processes and can be adapted with via middle and via last, F2F and F2B integration schemes.

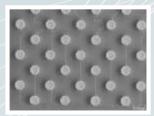

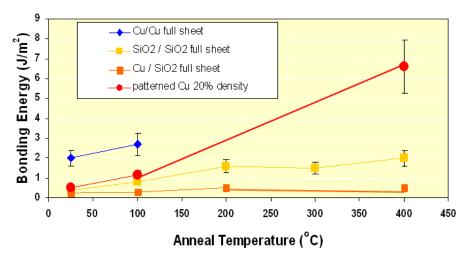

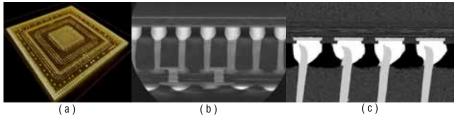

Copper pad sizes varying from 5µm to 500µm with a pitch of 10µm and 40µm were investigated, and excellent bonding interface defectivity was demonstrated (**Figure 3a**). Typically,

Figure 3a: Acoustic microscope image of the patterned Cu bonding interface (5x5µm Cu pad size and 10µm pitch, Cu density 20%) with 2h of annealing at 400°C

various interfaces are formed after patterned copper bonding. The bonding strength of the different types of interfaces has been evaluated (Figure **3b**). The highest bonding energy is obtained for copper-copper (Cu-Cu) interfaces, followed by SiO<sub>2</sub>-SiO<sub>2</sub>. The Cu-SiO<sub>2</sub> interface leads to the weakest adhesion even after 400°C annealing [6]. Copper interdiffusion and/or grain growth across the Cu-Cu bonded interface are the driving forces for achieving high bond strength [6, 8]. The achieved bonding strength has been sufficient to sustain post-processing such as silicon back thinning using coarse and fine grinding. In terms of electrical characterization, a specific contact resistance of 0.5Ω•μm² for a 10x10μm² contact area after annealing at 200°C

**Figure 3b**: Bonding energy evolution with temperature of different types of interfaces (Cu-Cu, Cu-Ox and Ox-Ox).

and 400°C for 2h was achieved [6, 11]. The resistance per node extracted from a ~30K daisy chain after 400°C post-bond anneal showed negligible resistance induced by bonding [11, 12]. In addition, initial reliability data based on electromigration (EM) testing shows that the bonded metallic interfaces are not the dominant path for the EM phenomena [13].

### **Stacking by Smart Cut**

Smart Cut technology [14] provides a path to monolithic 3D integration and enables the transfer of a blanket layer of single-crystal Si film onto a processed wafer (**Figure 4a**). On this new single-crystal Si surface, a second level of devices can be processed and this integration can be repeated in an iterative mode.

This technology benefits from existing high-volume manufacturing SOI infrastructure in addition to optimum donor wafer recycling techniques for lower cost-of-ownership.

Figure 4a: Process schematic of the Smart Cut Technology

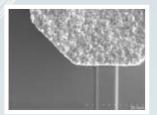

Compared to standard back thinning techniques, the Smart Cut atomic level splitting enables ultrathin (down to 0.1µm) layer transfer, thus simplifying and lowering the cost-of-ownership of the TSV process. The ultrathin transferred Si contributes to a smaller TSV aspect ratio that allows scaling to a

higher TSV density, or simply the use of more cost effective regular backend vias instead, thus making this technology attractive for applications that require higher interconnect densities.

This approach is based on our ability to optimize the bonding energy by diminishing the overall thermal budget

(as done for Smart Stacking) as well as optimizing the splitting kinetics to achieve splitting at low temperature  $(<350^{\circ}C)$  [5,15]. The transfer of the 200-400nm  $\pm 15$ nm top layer was demonstrated on a 300mm patterned wafer with low surface micro-roughness [8,16] (Figure 4b). The throughput of this process is slightly higher than the Smart Stacking process (~20-25 wafers/ hr) because stacking by Smart Cut does not require critical alignment. Devices formed on the new Si surface on top of the processed wafer will be constrained by the thermal budget limitation of the handle processed wafer.

Figure 4b: 300mm Si layer transfer demonstrated on patterned wafers (200nm  $\pm$  15nm transferred layer, RMS ~1.2Å  $2x2\mu m^2$ ).

### **Summary**