## MonolithIC 3D - General

By MonolithIC 3D Inc.

Issued March 2013

## **Contents**

| About the authors of the e-book                                                  | 5   |

|----------------------------------------------------------------------------------|-----|

| Part 1: Monolithic 3D - General                                                  | 11  |

| Chapter 1 - Is the Cost Reduction Associated with Scaling Over?                  | 12  |

| Chapter 2 - IEDM 2012 - The Pivotal Point for Monolithic 3D IC                   | 25  |

| Chapter 3 - The Monolithic 3D Advantage                                          | 34  |

| Chapter 4 - How can 3D be cheaper? Isn't it twice the cost?                      | 54  |

| Chapter 5 - Obtaining Monocrystalline Semiconductor Layers for Monolithic 3D     | 57  |

| Chapter 6 - Low Temperature Cleaving                                             | 59  |

| Chapter 7 - Low Temperature Wafer Direct Bonding                                 | 67  |

| Chapter 8 - How much does ion-cut cost?                                          | 74  |

| Chapter 9 - Is MonolithIC 3D-IC less risky than scaling or TSV?                  | 79  |

| Chapter 10 - The Future is the Interconnect: IITC                                | 85  |

| Chapter 11 - Can Heat Be Removed from 3D-IC Stacks?                              | 90  |

| Chapter 12 - 3D NAND Opens the Door for MonolithIC 3D                            | 97  |

| Part 2: 3D-CMOS: Monolithic 3D Logic Technology                                  | 104 |

| Chapter 13 – The Way and How of Fine-Grain 3D Integration                        | 105 |

| Part 3: 3D-FPGA: Monolithic 3D Programmable Logic                                | 113 |

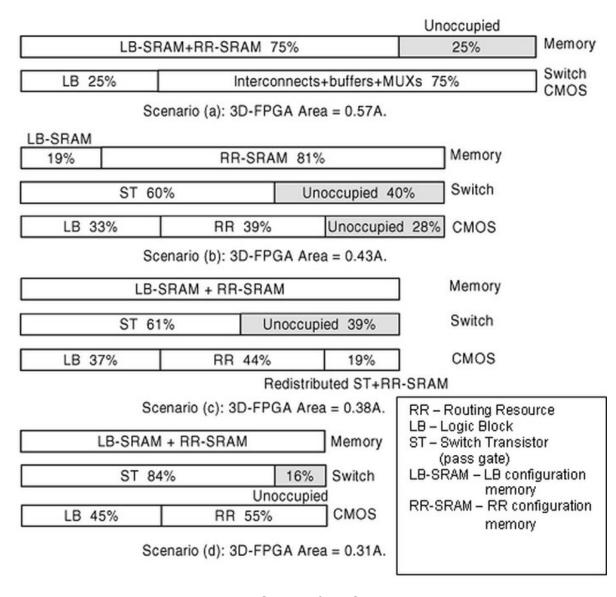

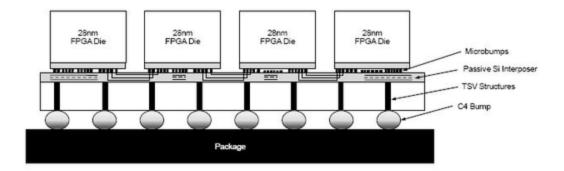

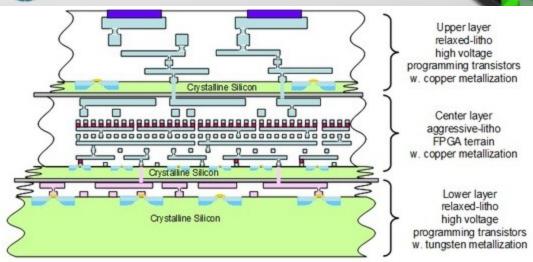

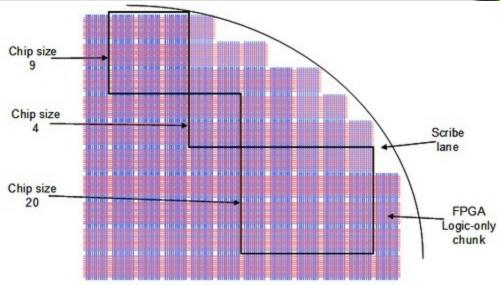

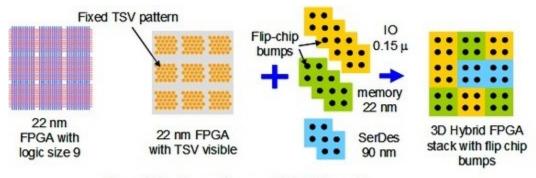

| Chapter 14 – Three Dimensional FPGAs                                             | 114 |

| Chapter 15 – Three Dimensional FPGAs – Part II                                   | 117 |

| Part 4: 3D-Gate Array: Monolithic 3D Gate Array                                  | 121 |

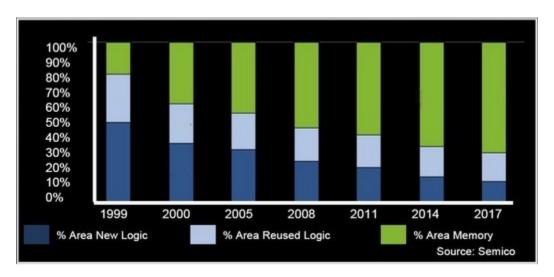

| Chapter 16 – Embedded Memory and MonolithIC 3D                                   | 122 |

| Part 5: 3D-Repair: Yield recovery for high-density chips                         | 127 |

| Chapter 17 – Can Yield Increase with 3D Stacking?                                | 128 |

| Chapter 18 – Monolithic 3D IC Could Increase Circuit Integration by 1,000x       | 130 |

| Chapter 19 – Repair in 3D Stack: The Path to 100% Yield with No Chip Size Limits | 134 |

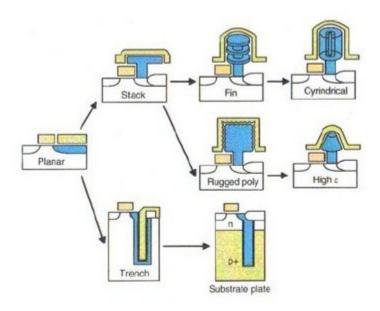

| Part 6: 3D – DRAM: Monolithic 3D DRAM                                            | 137 |

| Chapter 20 – Introducing our Monolithic 3D DRAM technology                       | 138 |

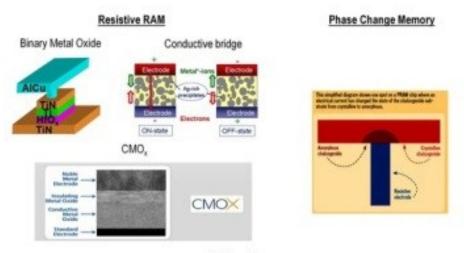

| Part 7: 3D – RRAM: Monolithic 3D RRAM                                            | 146 |

| Chapter 21 – Introducing our Monolithic 3D Resistive Memory Architecture         | 147 |

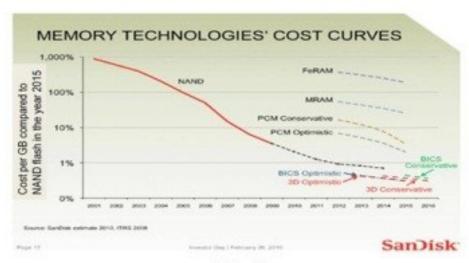

| Part 8: 3D – Flash: Monolithic 3D Flash Memory                                   | 157 |

| Chapter 22 – The Flash Industry's Direction and MonolithIC 3D Inc.'s Solution   | 158 |

|---------------------------------------------------------------------------------|-----|

| Part 9: IntSim v2.5                                                             | 163 |

| Chapter 23 – IntSim v2.0: An Open-Source Simulator for Monolithic 2D and 3D-ICs | 164 |

| Chapter 23 – Introducing IntSIm v2.5                                            | 168 |

### About the authors of the e-book

**Zvi Or-Bach**President and CEO

Zvi Or-Bach is the founder of MonolithIC 3D™ Inc., a Finalist of the "Best of Semicon West 2011" for its monolithic 3D-IC breakthrough. Or-Bach was also a finalist of the EE Times 2011 and 2012 Innovator of the Year Award for his pioneering work on the monolithic 3D-IC.

Or-Bach has a history of innovative development in fast-turn ASICs for over 20 years. His vision led to the invention of the first Structured ASIC architecture, the first single via programmable array, and the first laser-based system for one-day Gate Array customization. In 2005, Or-Bach won the EETimes Innovator of the Year Award and was selected by EE Times to be part of the "Disruptors" -- "The People, Products and Technologies That Are Changing The Way We Live, Work and Play".

Prior to MonolithIC 3D, Or-Bach founded eASIC in 1999 and served as the company's CEO for six years. eASIC was funded by leading investors Vinod Khosla and KPCB in three successive rounds. Under Or-Bach's leadership, eASIC won the prestigious **EE** Times' 2005 ACE Award for Ultimate Product of the year in the Logic and Programmable Logic category.

Earlier, Or-Bach founded Chip Express in 1989 (recently acquired by Gigoptix) and served as the company's President and CEO for almost 10 years, bringing the company to \$40M revenue, and to an industry recognition for three consecutive years as a high-tech Fast 50 Company that served over 1000 ASIC designs, including many one-day prototypes and one-week production delivery.

Even before his entrepreneurial ventures in ASIC technology, Or-Bach held engineering management positions at Elbit Computers, Ltd., Israel (subsidiary of Elron) and Honeywell (Lexington, Massachusetts). Zvi Or-Bach received his B.Sc. degree (1975) cum laude in Electrical Engineering from the Technion - Israel Institute of Technology, and M.Sc. (1979) with distinction in Computer Science, from the Weizmann Institute,

Israel. He holds over 100 issued or pending patents, primarily in the field of 3D integrated circuits and semi-custom chip architectures. He is the Chairman of the Board for Zeno Semiconductors, Bioaxial and VisuMenu. Or-Bach is passionate about the semiconductor industry, and has participated in <u>initiatives to improve immigration</u> and education policies to benefit the same.

**Brian Cronquist**Vice President, Technology & IP

Brian Cronquist has over 31 years of semiconductor industry experience, most recently as Sr. Dir. Technology Development & Foundry at non-volatile FPGA provider Actel. He has global experience on "both sides of the silicon wafer table": starting and building Chartered Semiconductor (Singapore) technology and customers as a captive then pure foundry, and non-volatile (antifuse and flash) FPGA technology at Actel as a fabless partner and customer to over 7 foundries and IDMs. He also led startup wafer fab engineering teams at Sierra Semiconductor, now PMC-Sierra, and developed new process technology at AMI and Synertek/Honeywell.

Mr. Cronquist has a diverse technical interest which includes developing ultra-thin thermal oxide and pre-cleaning technology (first to develop and implement HF-last), plasma etching of metals and oxides, database scaling techniques, process simulation & integration, novel ion implant techniques, first CMOS MOSFETs built with laser (CW) annealing, minimizing process induced damage PID) from plasma etching and ion implantation, time-to-market new product and process introduction (NPI), and customer engineering & program management.

While at Actel, he was also Principal Investigator of over \$24M of government funded technology programs developing radiation hardened (RH) versions of both anti-fuse and flash based product families in commercial and RH foundries. He has published over 85 technical papers in the fields of semiconductor microelectronic radiation effects and hardening, as well as new logic, antifuse & flash processes, devices, and reliability. Mr. Cronquist graduated cum laude (Chemistry Medal) in Chemistry from Santa Clara University in 1979. Currently, he is a visiting researcher at the Rice University Chemistry Department and an Industry Affiliate Partner at the Stanford University Nanofabrication Facility.

Ze'ev Wurman

Chief Software Architect

Wurman has over 30 years of experience in developing algorithms, CAD software, and hardware and software architectures. Before MonolithIC 3D Inc., he led the software development groups in DynaChip, an FPGA startup later acquired by Xilinx, and eASIC, a programmable logic company. Prior to that Wurman was the architect for hardware simulation accelerator at Amdahl, the largest and fastest hardware accelerator at the time. He designed and managed CAD software for Silvar-Lisco, and spent three years with IBM Research in Haifa, Israel, working on algorithms for design verification, databases, and cryptography. Between 2007 and 2009 Wurman served as senior policy adviser in the office of Planning, Evaluation, and Policy Development, in the U.S. Department of Education.

Wurman holds B.Sc. and M.Sc. degrees in Electrical Engineering from Technion, Israel Institute of Technology, in Haifa, Israel. He has published technical papers in professional and trade journals and holds seven patents.

**Israel Beinglass, Ph.D.**CTO Device Integration

Dr. Israel Beinglass has over 25 years of diversified experience in the semiconductor and semiconductor equipment industries. From 1989 through 2006 he was a senior technologist and business executive at Applied Materials (NASDAQ:AMAT), the global leader in semiconductor equipment, where he served in a variety of executive roles. He was General Manager of the High Temperature Films Group, Managing Director and Chief Technology Officer (CTO) for the Front End Equipment Group, and later CTO of Applied Global Services Group. He also served as the Chief Marketing Officer (CMO) of the CMP division and CTO for the Thin Films Group (TFG). Dr. Beinglass was involved in numerous successful acquisitions and was a member of Applied Materials Strategy and Marketing councils.

Dr. Beinglass is the industry pioneer of selective deposition; he is the co-inventor of the selective tungsten deposition process and an earlier developer of selective Epi deposition. He also was instrumental in developing the industry's first single-chamber polysilicon deposition system and an integrated, multi-chamber Policide system.

Before joining Applied Materials, Dr. Beinglass worked at Intel Corporation (NASDAQ:INTC) and IMP (NASDAQ:IMPX) in various positions, including process development manager and engineering manager of fab operations. While working at Intel he was the inventor of the selective tungsten deposition process. He was a corecipient of the Beatrice Winner Award for Editorial Excellence at the Intl. Solid State Circuits Conference in 1982. He serves as a board member at Noise Free Wireless and Spectros and used to serve as a board member at Silicon Genesis between 1998 and 2001.

Dr. Beinglass holds a Ph.D. in Materials Science from the Hebrew University of Jerusalem; he completed post-doctoral research at UCSF and is the holder of 30 US patents (288 citations) as well as several pending patents.

**Deepak Sekar, Ph.D.**Former Chief Scientist

Dr. Deepak Sekar received a B. Tech from the Indian Institute of Technology (Madras) in 2003 and a PhD from the Georgia Institute of Technology in 2008. He worked at SanDisk Corporation between 2006 and 2010, and conducted research on non-volatile memory. He joined MonolithIC 3D™ Inc. in early-2010 as a Principal Engineer, in 2011 as Chief Scientist of the company and left the company in March 2012.

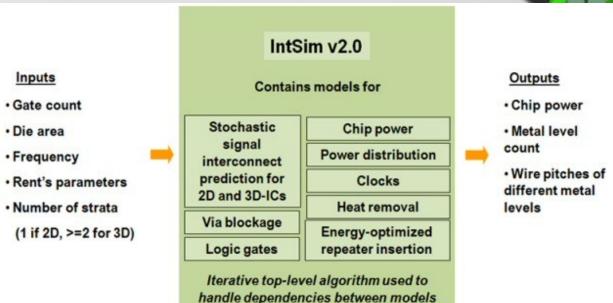

For the past 8 years, Dr. Sekar's research has focused on 3D Integrated Circuits. His PhD research involved doing some of the first experimental work on microchannel cooled 3D stacked chips. He also developed a CAD tool called IntSim that simulates 2D and 3D stacked systems. At SanDisk, Dr. Sekar worked in the area of 3D crosspoint memory and developed rewritable memory devices, selector diodes and array architectures.

Dr. Sekar is the author of a book, an invited book chapter, 15 publications and 55 issued or pending patents, predominantly in the field of 3D integration. Awards he has received include a Best Student Paper Award at the Intl. Interconnect Technology Conference (2008), a Best Paper Award at the IETE Technical Review (2009), an Intel PhD Fellowship (2006-2008), a Motorola Electronic Packaging Fellowship Award at the Electronic Components and Technology Conference (2008), two Inventor Recognition Awards from the Semiconductor Research Corporation (2006, 2009) and the National Talent Scholarship from the Government of India (1997-2003). He serves as a Program Committee Co-Chair at the International Interconnect Technology Conference and as an Advisory Board Member for 3D InCites.

## Part 1: Monolithic 3D - General

# Chapter 1 - Is the Cost Reduction Associated with Scaling Over?

by Zvi Or-Bach, the President and CEO of MonolithIC 3D Inc.

"Yes, unless we Augment Dimensional Scaling with monolithic 3D-IC Scaling"

The last 50 years of the semiconductor industry have been all about the manifestation of Moore's Law in dimensional scaling of Integrated Circuits (ICs). As consumers of electronic devices we all love to see with every new product cycle better products at a lower cost. But now storm clouds are forming, as was recently publicly expressed "Nvidia deeply unhappy with TSMC, claims 20nm essentially worthless".

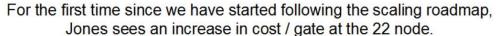

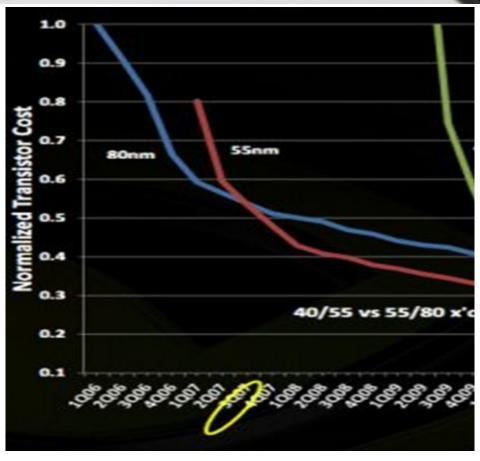

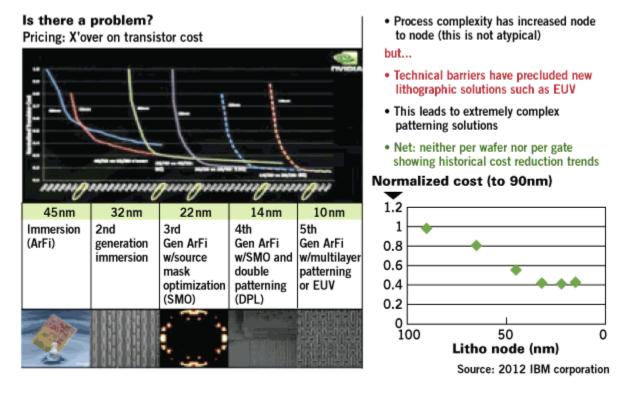

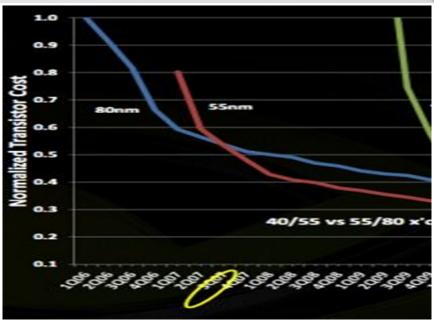

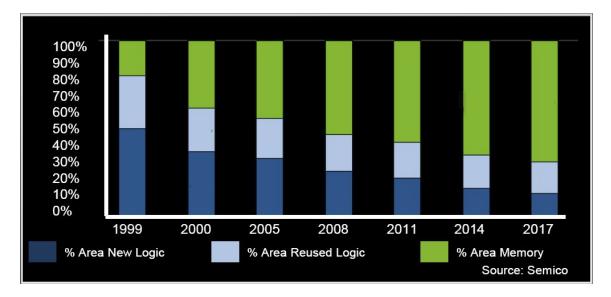

Clearly dimensional scaling is no longer associated with lower average cost per transistor. The chart below, published by IBS about a year ago, shows the diminishing benefit of cost reduction from dimensional scaling. In fact, the chart indicates that the 20nm node might be associated with higher cost than the previous node.

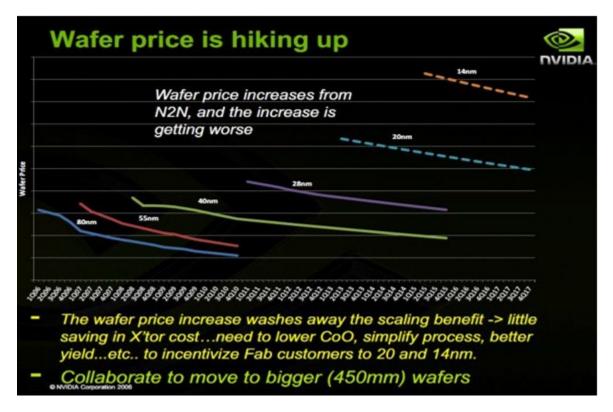

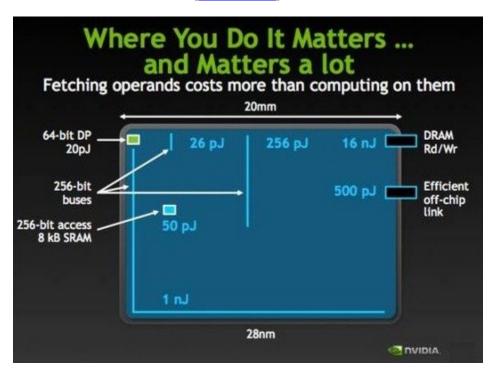

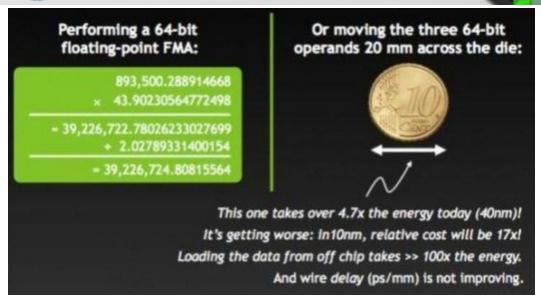

The following Nvidia chart provides the first order explanation. The cost reduction of dimensional scaling resulted from doubling the number of transistors per wafer. But if

the wafer cost of the new technology node increases by too much then it neutralizes that cost reduction. The Nvidia chart shows the wafer cost of recent nodes over time. In the past (...80nm, 55nm, 40nm) the incremental wafer cost increases were small and rapid depreciation of those costs resulted in almost constant average wafer price. Recent nodes (28nm, 20nm, 14nm,...), however, signal a new reality.

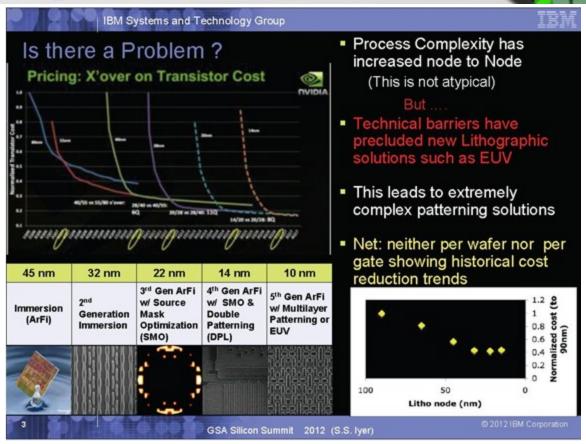

The following busy slide of IBM summarizes it clearly: "Net: neither per wafer nor per gate showing historical cost reduction trends"

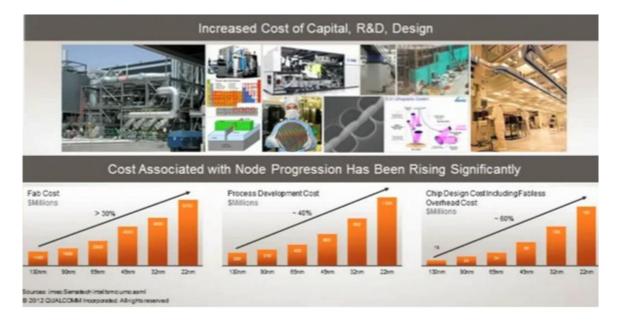

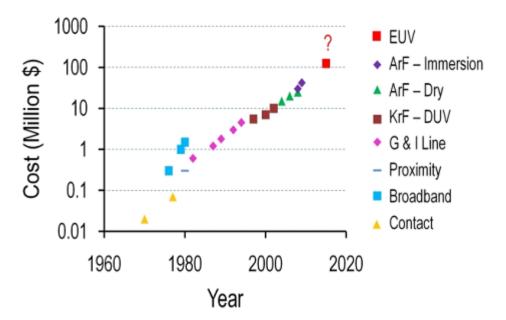

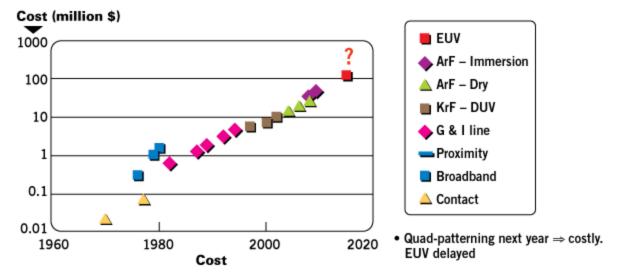

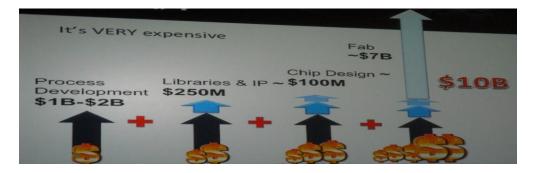

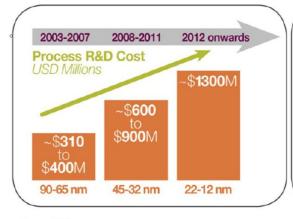

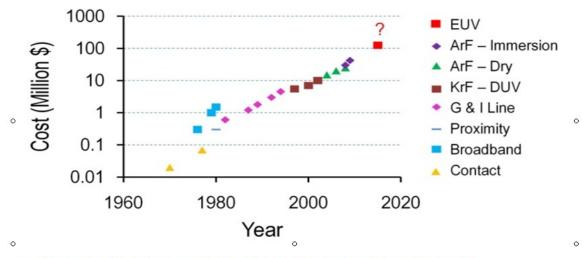

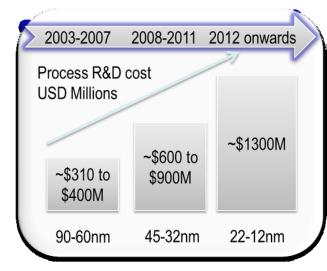

The number one driver to the increase of wafer cost is the increase in the equipment cost required for processing the next technology node. The following chart presents the increase in costs of capital, process R&D, and design.

The sharp increase of costs associated with scaling is a new phenomenon. There were always costs to move from one node to the next, but they were about constant or incrementally small.

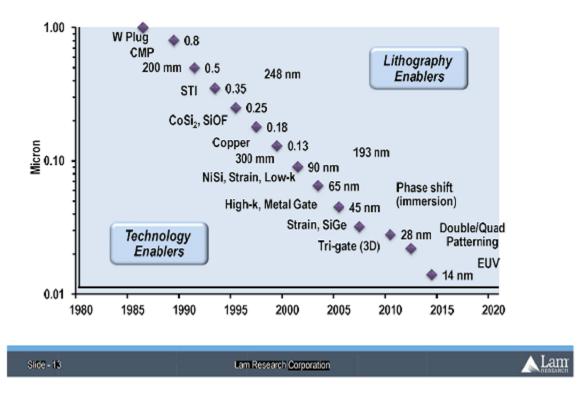

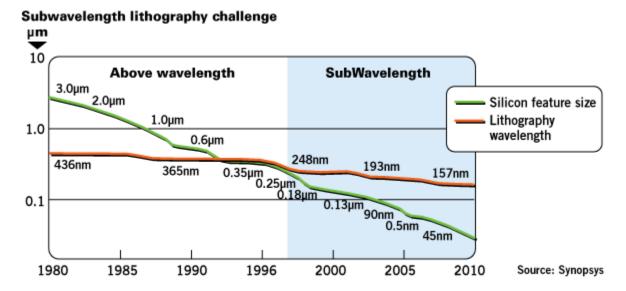

The following slide presents the innovations that enable dimensional scaling. Clearly, for many nodes we were able to use the same lithography tools. But once dimensional scaling reached the limit of light wavelength the lithography tool became critical and dominant. About for every node the lithography became a major challenge that required newer equipment and substantial process R&D. Moreover, in the recent lithography nodes the transistor itself required significant innovation at every node (high-k, Metal Gate, Strain, SiGe, Tri-gate,...) and it is clear that future scaled nodes will require even more of those innovations and their associated costs.

### Continuous Innovation Enables Continuation of Moore's Law

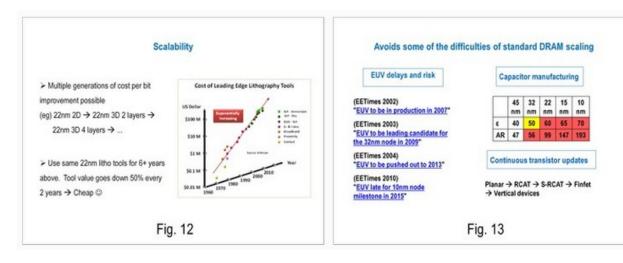

An important part of these costs is the escalating cost of the capital equipment for the next node fabrication lines. The following figure present the cost dynamic for the lithography equipment. Note the logarithmic scale of the cost axis.

Lithography tools grew from less than 10% of wafer fab equipment (WFE) spending to over 25% and accordingly lithography now represents about 50 % of the wafer cost.

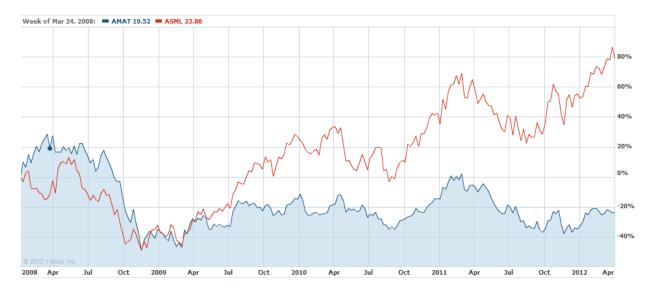

An interesting implication of growing domination of lithography in semiconductor processing is the fact that the ASML, which is the lead vendor of lithography tool, recently passed Applied Material's (the leader of all other tools) market cap. Following is the chart of the stock price of ASML (in red) vs. Applied Material (AMAT).

The clear conclusion of all of this is that future dimensional scaling is not about to change these trends. Accordingly, as stated in the IBM slide above: "Net: neither per wafer nor per gate showing historical cost reduction trends." Unless ...

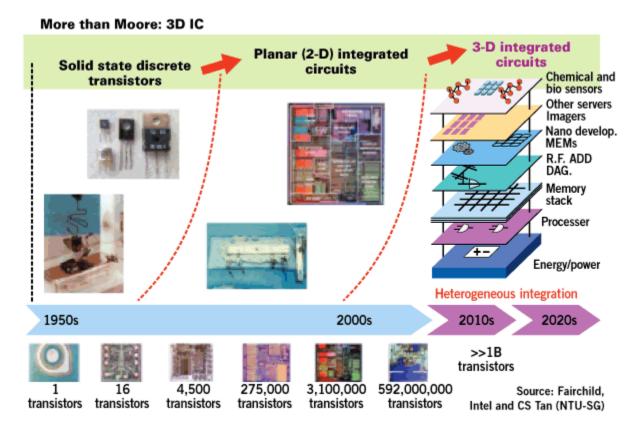

Unless we change the way we do scaling (remember Einstein's <u>famous quote</u>). Moore's Law is about doubling the number of transistors in a semiconductor device. At that time dimensional scaling was one of the three trends Moore described that would enable the observed and predicted exponential increase of device integration. It would seem that it is about time to look on another one of those - increasing the die size. If we do it by using the 3rd dimension – monolithic 3D-IC – we can achieve both higher integration and cost reduction!

It is not that we should stop scaling down, it just that if we augment it with scaling up we can introduce the required changes that can achieve the continuation of the cost reduction trend. Clearly almost all of the increases of wafer costs are related to the pace of dimensional scaling. If those costs could be spread over four years instead of two then the increase in wafer cost would be only about half of what it is now.

It might not be so clear, however, why monolithic 3D should reduce wafer cost. Shouldn't the cost of the double die size spread over two layers be at least double ...?

Monolithic 3D IC would reduce wafer cost because of the following elements:

- 1. Reduced Die Size It has been shown in many research studies that each folding into 3D has the potential to reduce the total required silicon area by 50% due to the reduced re-buffering and reduced sizing of the buffers.

- 2. Depreciation Scaling up enables the use of the same fab and process R&D for few additional years with the associated improvement in deprecation costs and improved manufacturing efficiencies and yield.

- 3. Heterogeneous Integration Scaling up would enable heterogeneous integration. This will open up the third trend of Moore- improved circuit design. As each strata of 3D IC could be processed in a different flow, cost and power could be saved by using a different process flow for logic, memory and I/O.

4. Multiple Layers Processed Together - This would be most effective for a memory type circuits. Using the right architecture, multiple transistors layers could be process simultaneously with the result of a huge reduction of cost per layer.

Let's detail each of these.

### **Reduced Die Size**

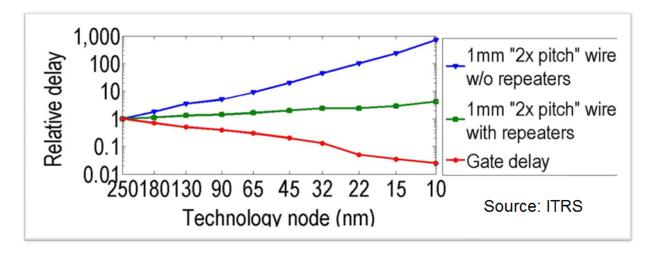

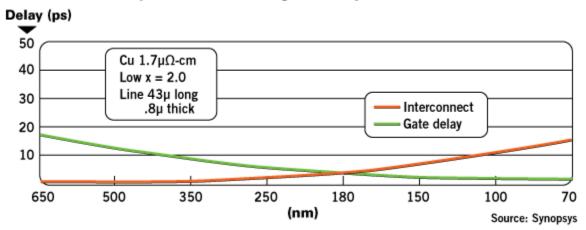

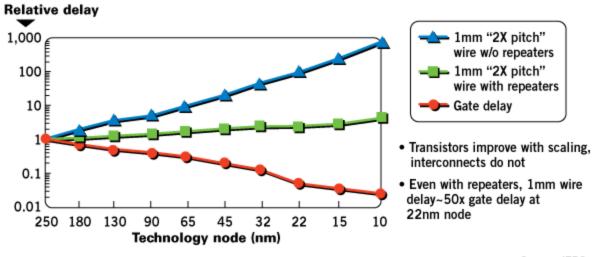

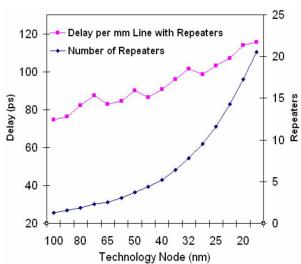

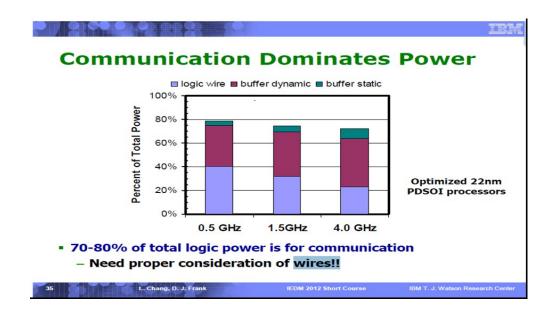

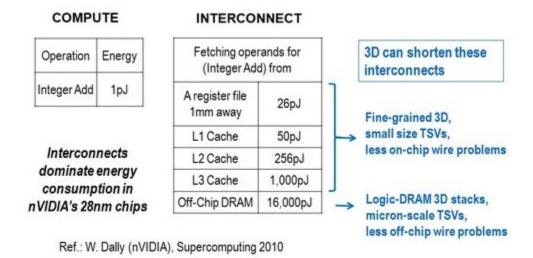

Dimensional scaling has always been associated with an increase of wire resistivity and capacitance. The industry had spent a huge effort to overcome these by first replacing the conducting material with copper and then changing the isolation material to low-K dielectrics. But the interconnect problem is still growing as demonstrated in the following chart.

- > Transistors improve with scaling, interconnects do not

- ➤ Even with repeaters, 1mm wire delay ~50x gate delay at 22nm node

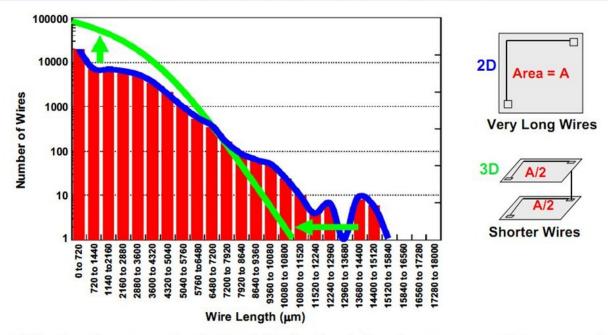

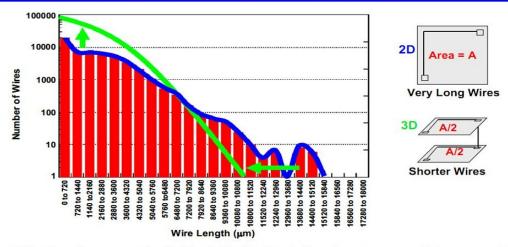

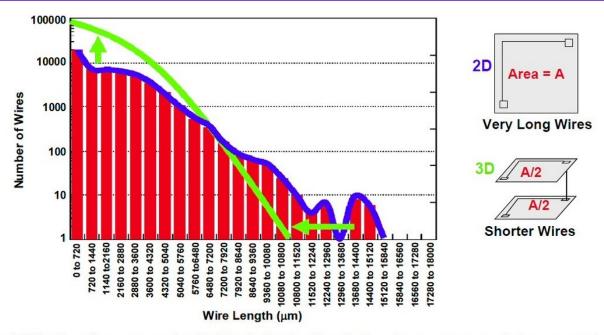

Every node of dimensional scaling is associated with larger cells, output drivers, and more buffers and repeaters. Monolithic 3D enables one to fold the circuit where the next strata is about  $1\mu$  above with a very rich vertical connectivity between the strata. The following IBM/MIT slide illustrates the effectiveness of such folding.

## Wire Length Distribution in 90 nm Node IBM Microprocessor\*

- >50% of active power (switching) dissipation is in microprocessor interconnects

- >90% of interconnect power is consumed by only 10% of the wires

\*After K. Guarini IBM Semiconductor Research and Development Center

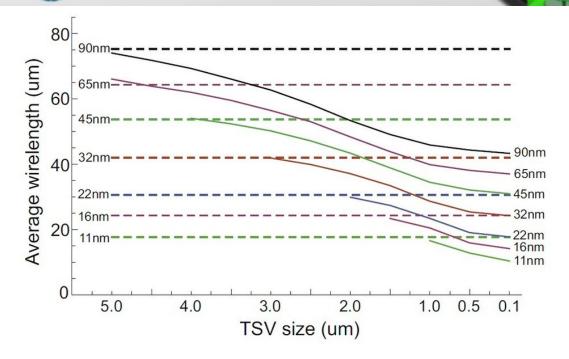

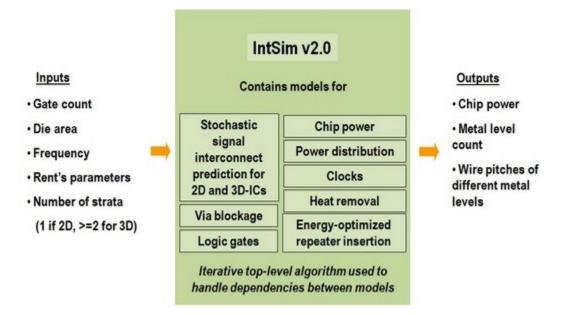

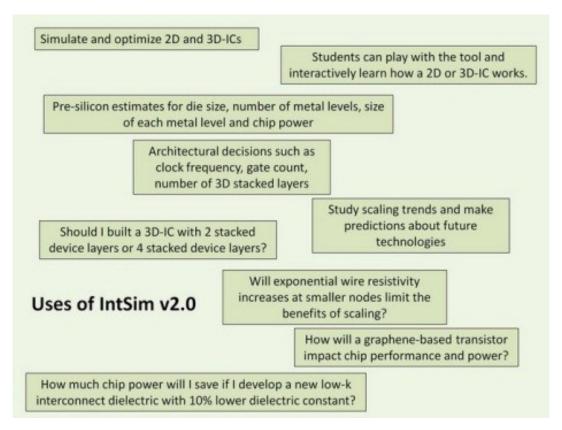

Further, the reduced silicon area generates an additional reduction of buffers and the average transistor size. MonolithIC 3D Inc. released an open-source top level simulator IntSim v2.0 to simulate a given design's expected size and power based on process parameters and the number of strata (more than 300 copies have been downloaded so far).

Using the simulator we can see in the following table that a design that uses 50 mm2 with average size gate size of 6 W/L, will need an average gate size of 3 W/L and accordingly only 24 mm2 if folded into two strata (the footprint will be therefore just 12 mm2).

| 22nm node<br>600MHz logic core | 2D-IC             | 3D-IC<br>2 Device<br>Layers | Comments                                                                                                        |

|--------------------------------|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| Metal Levels                   | 10                | 10                          |                                                                                                                 |

| Average Wire Length            | 6um               | 3.1um                       |                                                                                                                 |

| Av. Gate Size                  | 6 W/L             | 3 W/L                       | Since less wire cap. to drive                                                                                   |

| Die Size (active silicon area) | 50mm <sup>2</sup> | 24mm <sup>2</sup>           | 3D-IC → Shorter wires → smaller gates → lower die area → wires even shorter 3D-IC footprint = 12mm <sup>2</sup> |

| Power                          | Logic = 0.21W     | Logic = 0.1W                | Due to smaller Gate Size                                                                                        |

|                                | Reps. = 0.17W     | Reps. = 0.04W               | Due to shorter wires                                                                                            |

|                                | Wires = 0.87W     | Wires = 0.44W               | Due to shorter wires                                                                                            |

|                                | Clock = 0.33W     | Clock = 0.19W               | Due to less wire cap. to drive                                                                                  |

|                                | Total = 1.6W      | Total = 0.8W                |                                                                                                                 |

These results are in-line with many other monolithic 3D research results.

### **Depreciation**

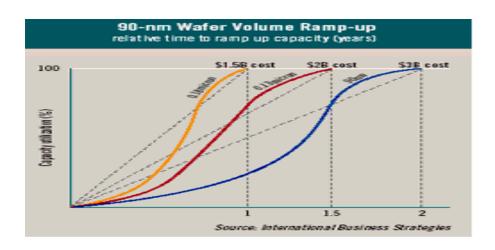

The semiconductor industry is very capital intensive and a very significant part of the wafer cost is associated with the cost of capital. Since every two years we have been scaling to a new node, then the wafer cost needs to support this rapid loss of capital value. Achieving the next level of device functionality using the same generation of tools allows for a far better utilization of the investment capital. In addition the learning curve of yield and manufacturing efficiency contributes further to the end-product cost reduction. The following chart portion demonstrates this well-known trend.

### **Heterogeneous Integration**

Let's start with quoting Mark Bohr, in charge of Intel's process development:

"Bohr: One important perspective is that chip technology is becoming more heterogeneous. If you go back 10 or 20 years ago, it was homogenous. There was a CMOS transistor, it was the same materials for NMOS and PMOS, maybe different dopant atoms, and that basic CMOS transistor fit the needs of both memory and logic. Going forward we'll see chips and 3D packages that combine more heterogeneous elements, different materials, and maybe transistors with very different structures whether they're for logic or memory or analog. Combining these very different devices onto one chip or into a 3D stack—that's what we'll see. It will be heterogeneous integration"

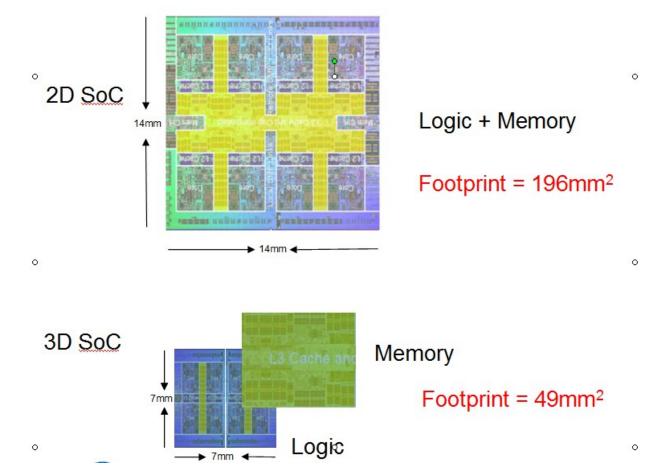

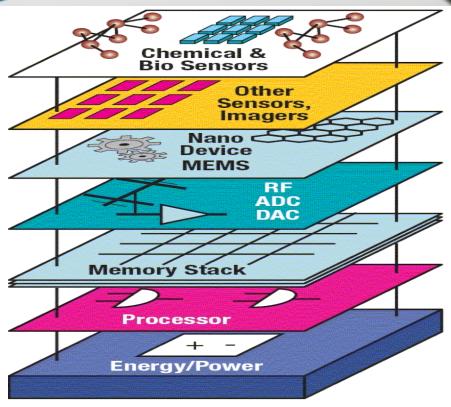

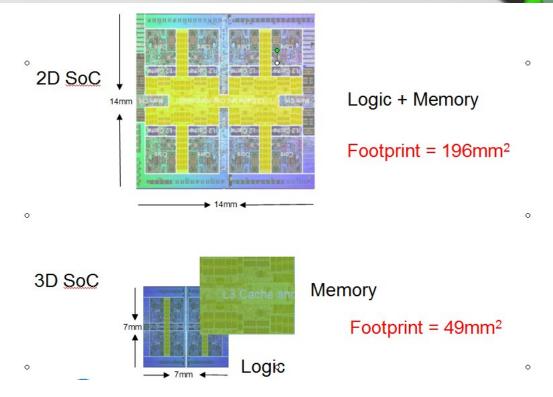

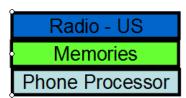

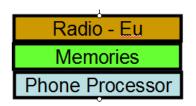

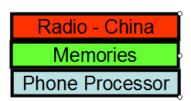

The most important market for semiconductor products is smart mobility. For this market the SoC device needs to integrate many functions. In most cases the pure high-performance logic would be about 25% of the die area, 50% would be memories and the rest would be analog functions such as I/O. In 2D they all need to be processed together and bear the same manufacturing costs. In a monolithic 3D-IC stack using

heterogeneous integration each stratum is processed in an optimized flow, allowing for a significant cost reduction. The following illustration suggests the use of only two strata to build a device that in 2D would have a size of 196 mm2. By having one stratum for logic and one for memory, and by using DRAM instead of SRAM, the device could be reduced to 98 mm2 with footprint of 49 mm2. The device cost would be further reduced by the memory using only 3 or 4 metal layers.

### **Multiple Layers Processed Together**

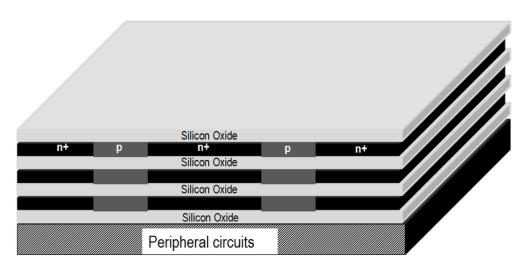

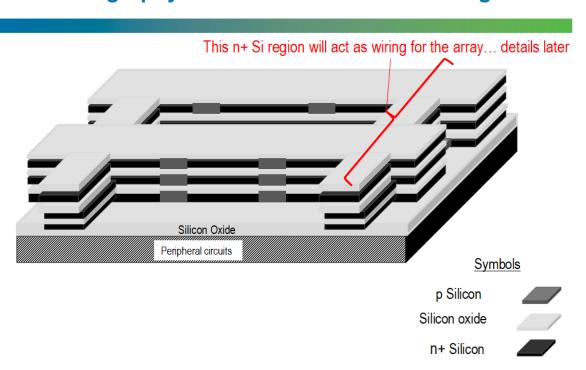

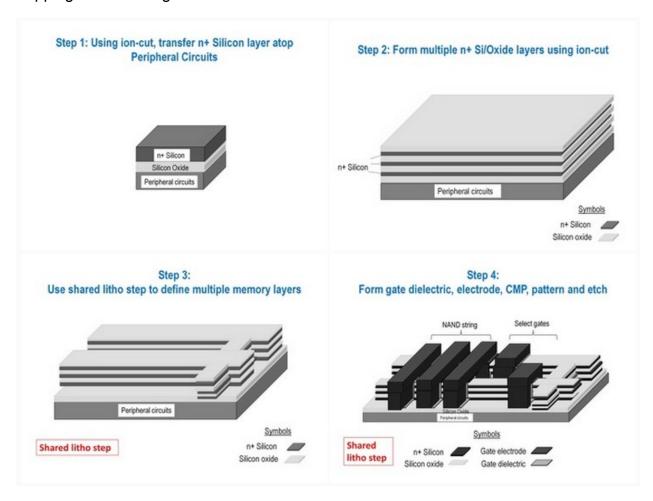

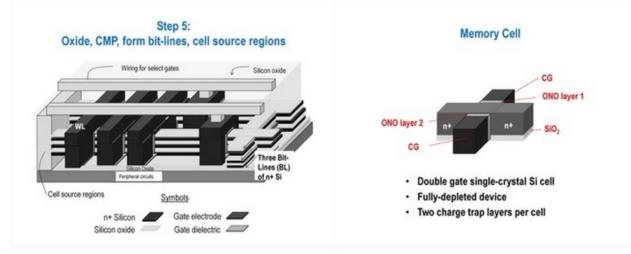

Using the right architecture, multiple transistor layers could be processed together with a huge reduction in cost per layer. This could be applied to many different types of regular devices.

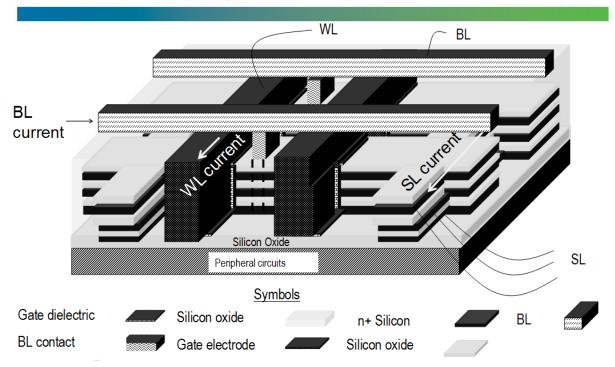

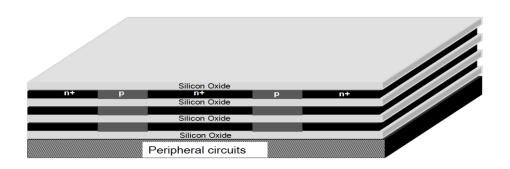

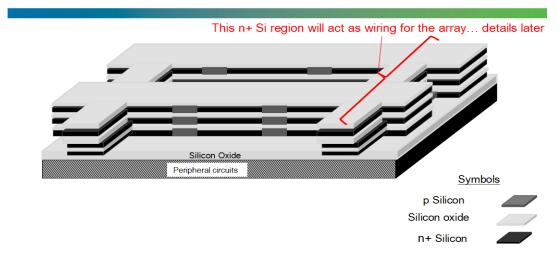

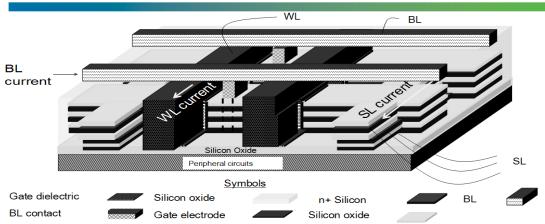

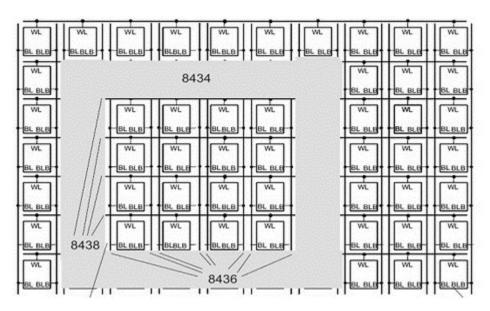

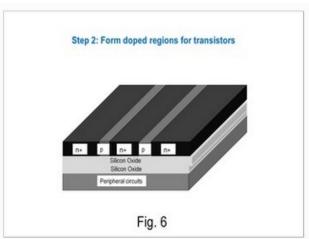

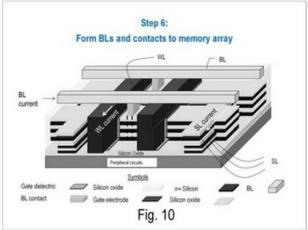

The following illustrate the concept with respect to a floating-body DRAM:

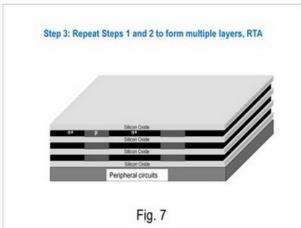

## **Process Flow: Step 6** Using methods similar to Steps 2-5, form multiple Si/SiO<sub>2</sub> layers, RTA

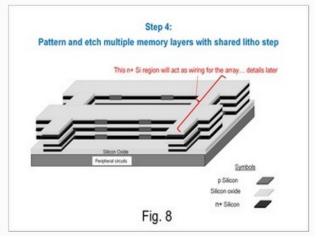

## **Process Flow: Step 7** Use lithography and etch to define Silicon regions

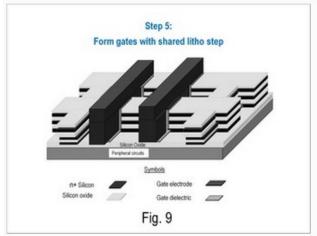

### **Process Flow: Step 11**

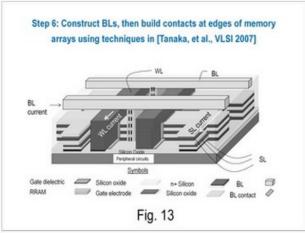

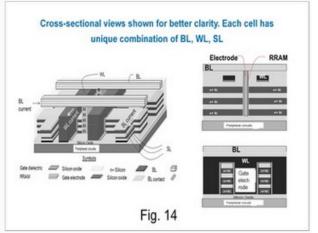

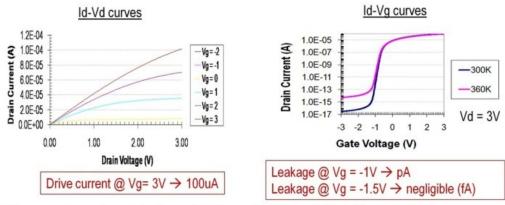

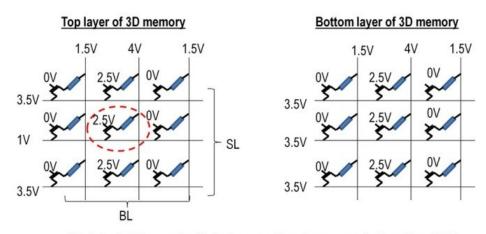

Construct BLs, then contacts to BLs, WLs and SLs at edges of memory array using methods in [Tanaka, et al., VLSI 2007]

MonolithIC 3D Inc's website presents more details for the DRAM flow, and also related flows for RRAM and NAND Flash memories.

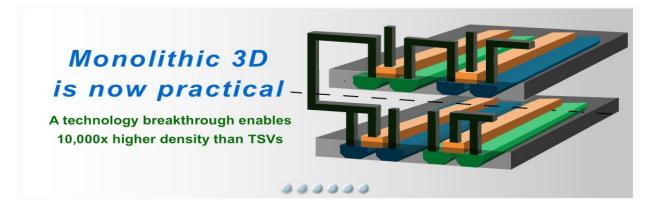

In short, we do have a path to continue the semiconductor industry drive for better products and with lower costs, but we should continuously apply innovation to do so. Now that monolithic 3D is practical, it is time to augment dimension scaling with monolithic 3D-IC scaling.

# Chapter 2 - IEDM 2012 - The Pivotal Point for Monolithic 3D IC

by Zvi Or-Bach, the President and CEO of MonolithIC 3D Inc.

From our biased point of view we see the recent IEDM12 as a pivotal point for monolithic 3D. Here's why:

We start with the EE Times article <u>IEDM goes deep on 3-D circuits</u>, starting with "Continuing on the theme of 3-D circuit technology addressed in an <u>earlier post</u> about this year's International Electron Device Meeting, Rambus, Stanford University and an interesting company called Monolithic 3D will address issues related to cooling 3-D circuits. .." and follow with a quote from the abstract to IEDMs short course "Emerging Technologies for post 14nm CMOS" organized by Wilfried Haensch, of IBM's Watson Research Center:

"Scaling the dimension was the key for the unprecedented success of the development of IC circuits for the last several decades. It now becomes apparent that scaling will become increasingly difficult due to fundamental physical limits that we are approaching with respect to power and performance trade-offs. This short course will give an overview of several aspects in this "end-of-scaling" scenario. ..."

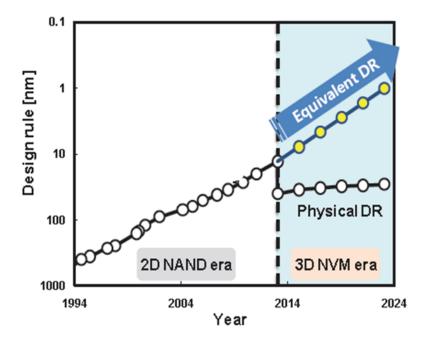

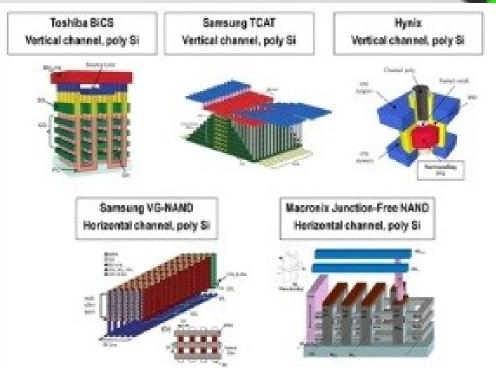

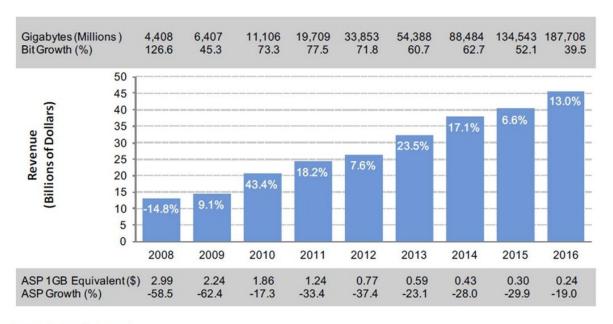

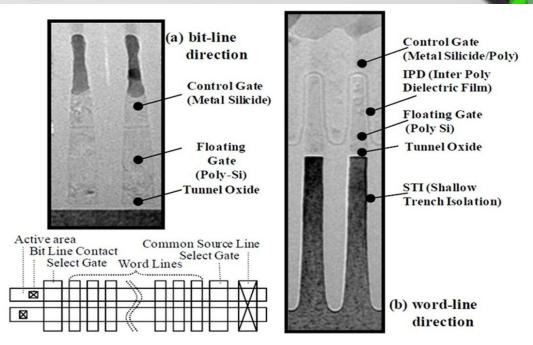

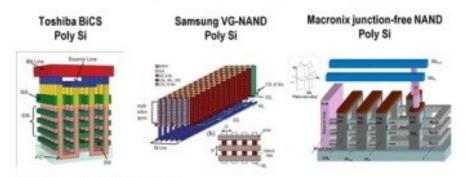

We then continue with statements made by Dr. Howard Ko, a Senior Vice President and General Manager of the Silicon Engineering Group of Synopsys in his 2013: Next-generation 3-D NAND flash technology article:

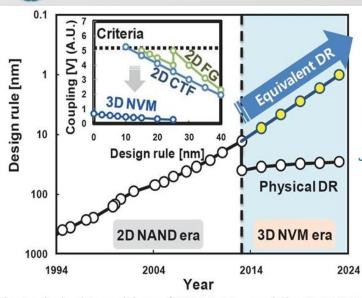

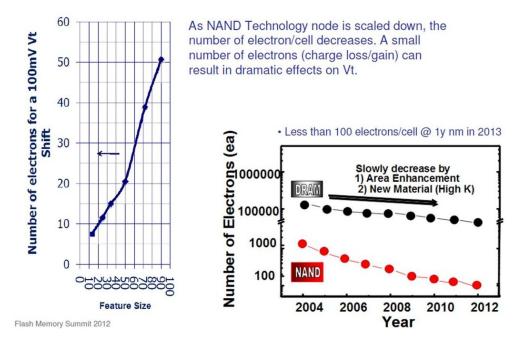

"Yet there are a variety of developments in another type of 3-D scaling that are likely to have a similarly large impact on semiconductors in the near future - 3-D devices for NAND flash.... And as in planar CMOS logic, NAND flash technology has been progressively scaled to smaller feature sizes, becoming the process leader in driving the smallest line-widths in manufacturing as evidenced by the current 1x-nm (~19-nm) process node. Yet, despite plans to scale down to the 1y-nm (~15-nm) and possibly 1z-nm (~13-nm) nodes, the traditional planar floating gate NAND flash architecture is approaching the scaling limit, prompting the search for new device architectures. Not to be upstaged by the planar to 3-D (FinFET) transition in logic devices, NAND flash has embarked on its own 3-D scaling program, whereby the stacking of bit cells allows continuous cost-per-bit scaling while relaxing the lateral feature size scaling."

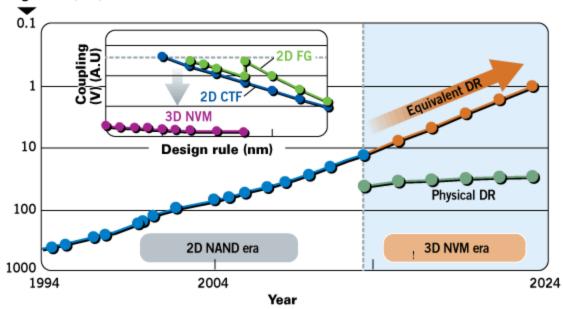

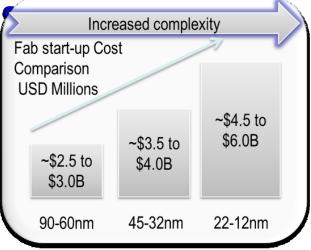

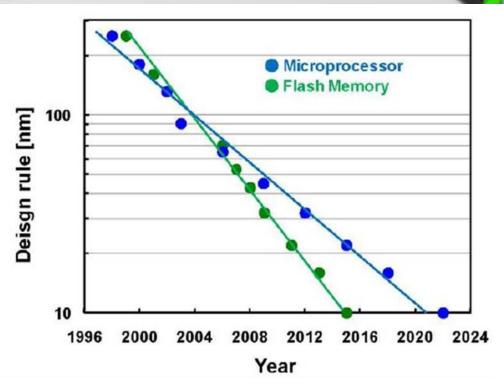

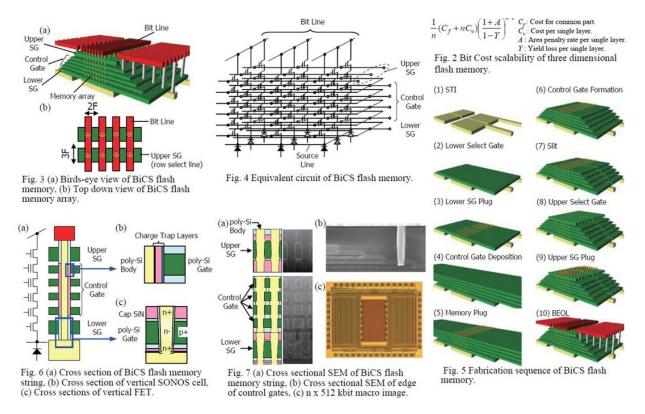

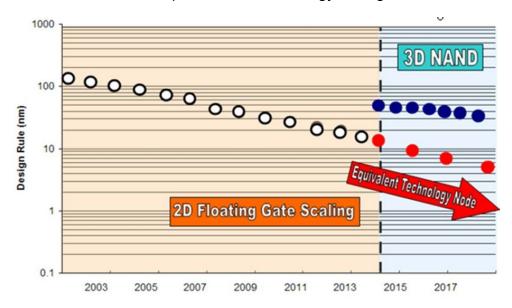

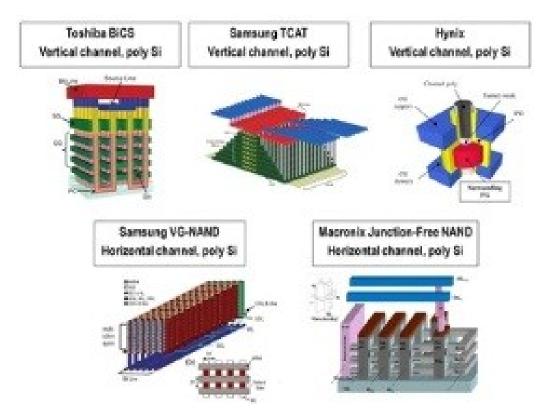

In our recent blog <u>3D NAND Opens the Door for Monolithic 3D</u> we discussed in detail the adoption of monolithic 3D for the next generations of NAND Flash. The trend was very popular subject of this year's IEDM and is nicely illustrated by this older chart:

### In 2D-to-3D paradigm shift, challenges = opportunities

### Design rule (nm)

- By 2013, 3D NAND flash is going into commercialization. This will be the biggest paradigm shift in NVM business.

- . To make 3D NAND flash happen, collaboration should be considered.

Source: Jungdai Choi, et al., (Samsung), VLSI 2011

And accordingly the updated ITRS 2012 present the change from dimension scaling to monolithic 3D scaling as presented in the following slide.

## 2012 Update: Non-Volatile Memory

Based on survey performed by Japan PIDS, completed in March 2012, together with market observations.

- Compared to 2011 Edition, half-pitch scaling is unchanged.

- Some revisions for FeRAM (cell size, switching charge density...).

| NAND Flash                                                       |      |      |           |           |                |                |                |              |              |              |            |            |            |            |

|------------------------------------------------------------------|------|------|-----------|-----------|----------------|----------------|----------------|--------------|--------------|--------------|------------|------------|------------|------------|

| Year of Production                                               | 2012 | 2013 | 2014      | 2015      | 2016           | 2017           | 2018           | 2019         | 2020         | 2021         | 2022       | 2025       | 2024       | 2025       |

| Uncontacted poly 1/2 pitch<br>(min)                              | 20   | 18   | 17        | 15        | 14             | 13             | 12             | 11           | 10           | 9            | 8          | 8          | 8          | 8          |

| Number of word lines in one<br>NAND string                       | 84   | 64   | 64        | 64        | 64             | 64             | 64             | 64           | 64           | 64           | 64         | 64         | 64         | 64         |

| Dominant Cell type                                               | FG   | FG   | FG/C<br>T | FG/C<br>T | CT-<br>3D      | CT-<br>3D      | CT-<br>3D      | CT-<br>3D    | CT-<br>3D    | CT-<br>3D    | CT-<br>3D  | CT-<br>3D  | CT-<br>3D  | CT-<br>3D  |

| Maximum number of bits per<br>chip (SLC/MLC)                     |      |      |           |           | 128G /<br>256G | 256G /<br>512G | 256G /<br>512G | 512G /<br>1T | 512G /<br>1T | 512G /<br>1T | 1T /<br>2T | 1T /<br>2T | 1T /<br>2T | 2T /<br>4T |

| Minimum array 1/2 pitch -<br>F(mm) [15]                          |      |      |           |           | 32nm           | 32nm           | 32nm           | 28nm         | 28nm         | 28nm         | 24nm       | 24nm       | 24nm       | 18nm       |

| Number of 3D layers for array<br>at minimum 1/2 array pitch [16] |      |      |           |           | 8              | 16             | 32             | 32           | 64           | 64           | 98         | 98         | 98         | 128        |

ITRS Winter Public Conf/Dec. 5, 2012/Hsinchu, Taiwan

This year's IEDM brought up two of the driving forces behind the shift from dimensional scaling to monolithic 3D IC scaling, that we will detail below as #1 and #2.

The Current 2D-IC is Facing Escalating Challenges:

### On-chip interconnect (#1)

- Dominates device power consumption

- Dominates device performance

- Penalizes device size and cost

### Lithography (#2)

- Dominates Fab cost

- Dominates device cost and diminishes scaling benefits

- Dominates device yield

- Dominates IC development costs

The problem with on-chip interconnect didn't start today. This vintage Synopsys slide below clearly indicates that on-chip interconnect started to dominate overall device performance a decade ago:

### Interconnect delay creates the timing closure problem

In response, the industry has spent an enormous amount of money to convert from aluminum to copper and to low-K inter-metal dielectrics. But now, we have very few additional options left (perhaps air-bridge?) as illustrated by the following chart:

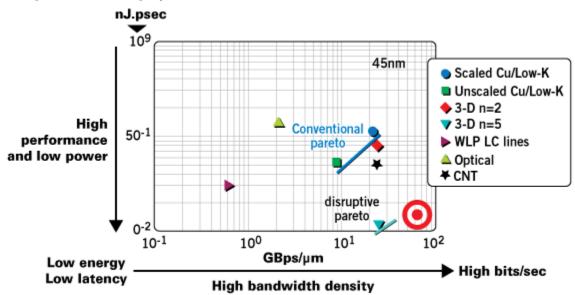

### E-D product vs. Gbps/µm for 1mm

- 3-D with 5 strata clearly gives the highest bandwidth density for the lowest energy delay product.

- No other technology options give significant advantages over conventional scaled or unscaled Cu/Low k.

Source: Scott List, IMEC (M. Bamal, et al., IITC2006)

It shows that neither Carbon Nano Tube (CNT) nor Optical interconnect are better than copper, and that monolithic 3D still is the best path.

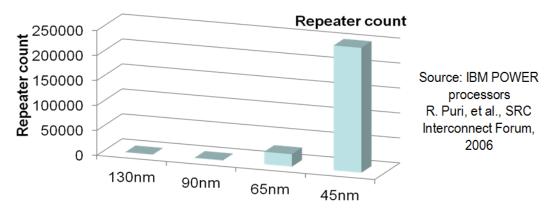

The practiced 'band-aid' fix so far has been throwing more transistors (they are getting cheaper, right? No longer. See father below) at the problem in the form of buffer and repeaters. But as we scale down we need exponentially more of these ban-aids as illustrated by the following:

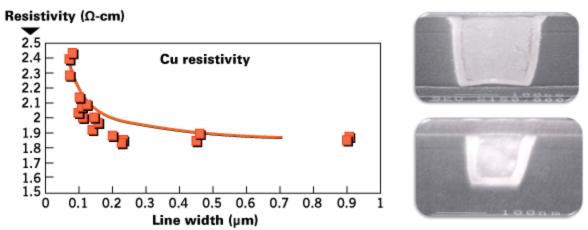

Copper, however, is now reaching its inflection point as was articulated in a special session organized by Applied Materials attached to this IEDM, The 14 nanometer node is expected to be an inflection point. Quoting from the abstract:

"The 14 nanometer node is expected to be an inflection point for the chip industry, beyond which the resistivity of copper interconnects will increase exponentially and may become a limiting factor in chip design. On December 11, 2012, Applied Materials, Inc. will host an important forum in San Francisco to explore the path that interconnect technology must take to keep pace with transistor scaling and the transition to new 3D architectures." (emphasis added)

This had been illustrated before in the following chart

- . Barrier layer takes a big part of the conducting area increase resistivity

- · Copper grain effect significantly increase resistivity

Source: Sam Naffziger, AMD Fellow at 2011 VLSI Symposium Keynote

And to make it crystal clear, IBM presented the following chart in its short course:

Power is now dominating IC design and clearly dimensional scaling does not improve the interconnect's impact – see the following chart built from the ITRS Roadmap. The only effective path forward that addresses interconnect is monolithic 3D.

Source: ITRS

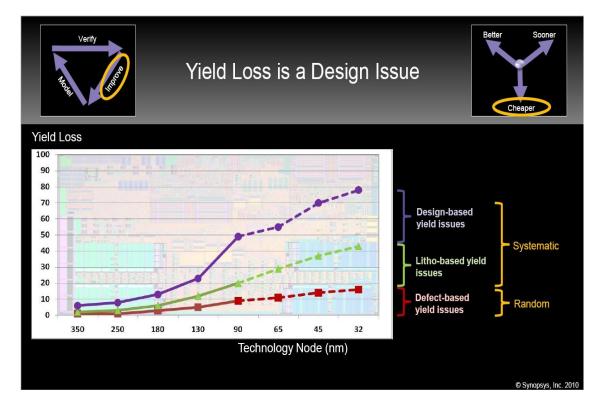

As for the second challenge – lithography – we start again with an old chart by Synopsys:

The implication is that any new node of dimensional scaling comes with escalating lithography costs; and sure enough, that's what is happening. When litho costs are plotted over time, it fits a log-linear scale....this is not a sustainable trend.

The following chart illustrates the lithography escalating cost of equipment which directly reflect the wafer cost.

This resulted in the following slide by IBM at the GSA Silicon Summit 2012:

Quoting from the slide: "Net: neither per wafer nor per gate [are] showing historical cost reduction trends"

Another EE Times IEDM12 article covering a keynote given by Luc van den Hove, chief executive of IMEC, <u>IEDM: Moore's Law seen hitting big bump at 14 nm</u>, repeats the same conclusion. In fact, some vendors are already changing course accordingly. GlobalFoundries, in its recent 14nm announcement, disclosed that the back-end will be unchanged from 20nm. This suggests a similar die size and respective

increase in per-transistor cost. Further, ST Micro in the Fully Depleted Transistors Technology Symposium (11 December, 2012) during IEDM12 week also acknowledged that their 14nm node will have a 20nm node metal pitch, and, just like GlobalFoundries, a similar die size and increase in per-transistor cost. So it would seem that also for lithographic reasons, the industry's next generation path, and the continuation of Moore's Law, would be achieved by leveraging the third dimension.

Now that monolithic 3D is feasible and practical, the time has come to move in this new direction, as has been nicely illustrated by this concluding chart below

### **Chapter 3 - The Monolithic 3D Advantage**

by Zvi Or-Bach, the President and CEO of MonolithIC 3D Inc.

### 1. Introduction

Over the last 50 years we have seen tremendous technological and economic progress in semiconductors and microelectronics following what is known as Moore's Law. Accordingly about every two years the amount of transistors we can integrate on an IC doubles. This exponential increase in integration is achieved by scaling down the dimensions of the microcircuit by a factor of 0.7 at every technology node. For most of that half-century the scaling was relatively easy and was associated with about a 30% reduction of the transistor cost, a greatly improved performance, and markedly reduced power consumption. For most of us who have lived and worked this scaling - 'those were the days!'

However, recently the trend has changed dramatically, and it is now harder and harder (technically and economically) to achieve dimensional scaling; and as a result, there are diminishing improvements in transistor costs, power or performance. We discuss many of the details on our blogs:

IEDM: Moore's Law seen hitting big bump at 14 nm

Is the Cost Reduction Associated with Scaling Over?

Entanglement Squared

IEDM 2012 - The Pivotal Point for Monolithic 3D IC

A new form of scaling is shaping up as an alternative to maintain the exponential increase in integration. This new form is scaling up using monolithic 3D technology. The NAND Flash vendors are the early adopters of this new alternative scaling with multiple variations of products being developed that are scheduled to reach volume production in 2015.

In the following we will present "The Monolithic 3D" advantage. It is possible that this new technology could return us to the trend we had enjoyed before with reductions of cost, decreases in power consumption, and improvements in performance, and bring some new and compelling benefits.

### Specifically, these are:

- Continuing reductions in die size and power

- Significant advantages for reusing the same fab line and design tools

- Heterogeneous Integration

- > Processing multiple layers simultaneously, offering multiples of cost improvement

- Logic redundancy, allowing 100x integration at good yields

- Modular Platforms

### 2. Reduction in die size and power

### A. Reduction in die size

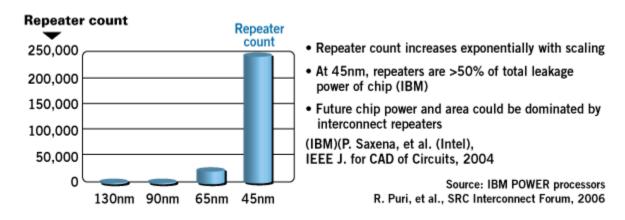

Dimensional scaling has always been associated with increased wire resistivity and capacitance. Every node of dimensional scaling is associated with larger output drivers and more buffers and repeaters. The following charts illustrate the rapid increase of the number of transistors associated with the increased interconnect challenge.

Figure 6. Global interconnection delay per mm length with repeaters.

Source: ISQED07 Alam

- Repeater count increases exponentially with scaling

- > At 45nm, repeaters are >50% of total leakage power of chip [IBM].

- ➤ Future chip power & area could be dominated by interconnect repeaters [IBM][P. Saxena, et al. (Intel), IEEE J. for CAD of Circuits, 2004]

Monolithic 3D enables the folding of a circuit, with the each stratum only about  $1\mu$  above or below its neighbor, combined with a very rich vertical connectivity between the strata. The following IBM/MIT slide illustrates the effectiveness of such a folding.

#### Wire Length Distribution in 90 nm Node IBM Microprocessor\*

- · >50% of active power (switching) dissipation is in microprocessor interconnects

- >90% of interconnect power is consumed by only 10% of the wires

\*After K. Guarini IBM Semiconductor Research and Development Center

Further, the reduced silicon area generates an additional reduction of buffers and the average transistor size. MonolithIC 3D Inc. released an open-source high level simulator IntSim v2.0 to simulate a given design's expected size and power based on process parameters and the number of strata. More than 400 copies have been downloaded so far.

Using the simulator we can see in the following table that a 2D design of 50 mm2 area with an average gate size of 6 W/L, will only need an average gate size of 3 W/L and accordingly only 24 mm2 of total circuit area if folded into two strata (the footprint will be therefore just 12 mm2).

| 22nm node<br>600MHz logic core | 2D-IC             | 3D-IC<br>2 Device<br>Layers | Comments                                                                                            |

|--------------------------------|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| Metal Levels                   | 10                | 10                          |                                                                                                     |

| Average Wire Length            | 6um               | 3.1um                       |                                                                                                     |

| Av. Gate Size                  | 6 W/L             | 3 W/L                       | Since less wire cap. to drive                                                                       |

| Die Size (active silicon area) | 50mm <sup>2</sup> | 24mm²                       | 3D-IC → Shorter wires → smaller gates → lower die area → wires even shorter 3D-IC footprint = 12mm² |

| Power                          | Logic = 0.21W     | Logic = 0.1W                | Due to smaller Gate Size                                                                            |

|                                | Reps. = 0.17W     | Reps. = 0.04W               | Due to shorter wires                                                                                |

|                                | Wires = 0.87W     | Wires = 0.44W               | Due to shorter wires                                                                                |

|                                | Clock = 0.33W     | Clock = 0.19W               | Due to less wire cap. to drive                                                                      |

|                                | Total = 1.6W      | Total = 0.8W                |                                                                                                     |

These results are in-line with many other monolithic 3D research results.

=> Monolithic 3D 'folding' reduces the device silicon size by ~50% and leads to a similar reduction in transistor cost.

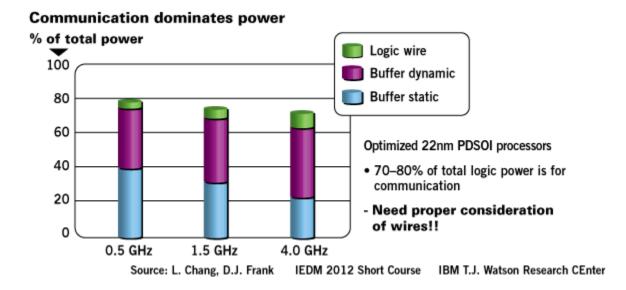

#### B. Reduction in power

The following chart illustrates that interconnect is now dominating the device power.

=>As every 'folding' effectively reduces the average wire length by about 50% it results in reducing the average power by 50%.

(Note: This assumes a proportional increase in complexity, which the industry has consistently done)

#### 3. Significant advantages for using the same fab and design tools

#### A. Depreciation

With dimensional scaling every technology/process node requires a significant capital investment for new processing equipment, significant R&D spending for new transistor

process and device development, and the building of an ever more complex and costly library and EDA flow. The following charts illustrate this escalating cost trend:

Januar 2010

Courtesy: GlobalFoundries

With monolithic 3D these costs are not required as dimensions are maintained for multiple generations and only the number of strata or layers is increased.

If the industry could use the same equipment and the same transistors and libraries for 4 years instead of 2, then all these costs could be depreciated over a longer time, with resulting significant cost benefits.

The following chart portion demonstrates the reduction of transistor cost per node as yield improves and equipment cost depreciates

#### B. Learning Curve - Yield

Using the same transistor tools and EDA has an additional important benefit. Learning curve equals yield improvement. With dimensional scaling we face the predicament that by the time we know how to manufacture a process node well, that learning quickly becomes obsolete as we are quickly moving on to the next node.

With monolithic 3D, the learning of the previous node stacking is directly utilized on the integration development of more strata, rather than on new materials, design tool issues, etc.

The following chart illustrates the dimensional scaling trend:

Each node of scaling is taking longer and costing more to get to mature yield ('ramped-up')

The design and litho based yield loss is growing quickly as the technology node gets dimensionally smaller.

#### 4. Heterogeneous Integration

3D IC enables far more than an alternative for increased integration. It provides another dimension of design flexibility.

A well-known aspect of this flexibility is the ability to split the design into layers which could be processed and operated independently, and still be tightly interconnected - especially for monolithic 3D.

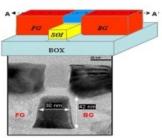

The following figure illustrates the ability to use different substrate crystal and different type of devices in such a heterogeneous integration.

#### A. Logic, Memory, IO

Let's start with quoting Mark Bohr, in charge of Intel's process development:

"Bohr: One important perspective is that chip technology is becoming more heterogeneous. If you go back 10 or 20 years ago, it was homogenous. There was a CMOS transistor, it was the same materials for NMOS and PMOS, maybe different dopant atoms, and that basic CMOS transistor fit the needs of both memory and logic. Going forward we'll see chips and 3D packages that combine more heterogeneous elements, different materials, and maybe transistors with very different structures whether they're for logic or memory or analog. Combining these very different devices onto one chip or into a 3D stack—that's what we'll see. It will be heterogeneous integration"

The most important market for semiconductor products is smart mobility. For this market the SoC device needs to integrate many functions, such as logic, memory, and analog. In most cases the pure high-performance logic would be about 25% of the die

area, 50% of the area would be memory, and the rest would be analog functions such as I/O, RF, and sensors.

In 2D all the functions need to be processed together and bear the same manufacturing costs. In a monolithic 3D-IC stack using heterogeneous integration each stratum is processed in an optimized flow, allowing for a significant cost reduction and no loss in optimized performance for each function type. The following illustration suggests the use of only two strata to build a device that in 2D would have a size of 196 mm2. By having one stratum for logic and one for memory, and by using DRAM instead of SRAM, the device could be reduced to 98 mm2 with footprint of 49 mm2. The device cost would be further reduced by the memory using only 3 or 4 metal layers. <a href="eDRAM">eDRAM</a> on logic

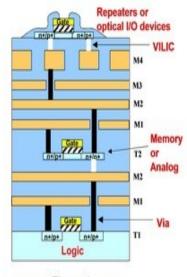

#### B. Strata of Logic

The logic itself could be constructed better using heterogeneous integration. In many cases only portion of the logic need to be high performance while other portion could be better – and cheaper – done using older process node. Other scenarios could include designing different strata with different supply voltages for power savings, different number of metal interconnect layers, or other variations in the design space.

#### C. Strata of different substrate crystals and fabrication processes.

3D enabled heterogeneous integration could be used as illustrated in the beginning of the chapter. Some layers could utilize silicon while other might use compound semiconductors. Some layers could be image sensors or other type of electro-optic structures and so forth.

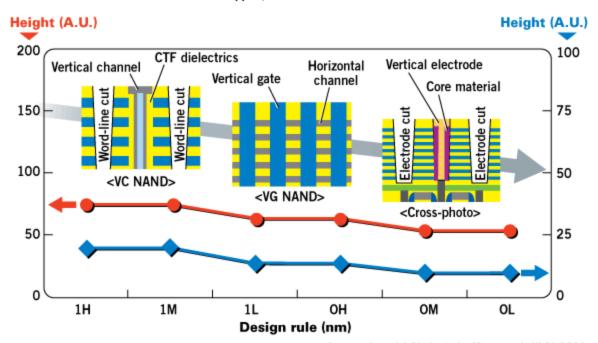

#### 5. Multiple Layers Processed Simultaneously

An extremely powerful unique advantage of monolithic 3D is the option to process multiple layers in parallel following one lithography step. This option is most natural for regular circuits such as memory, but it is also available for logic circuits.

The driver for this option is the escalating costs of lithography in state of the art IC. The following illustration presents the impact of dimensional scaling on lithography costs.

Quad-patterning next year → costly. EUV delayed, costly.

Currently the critical lithography steps dominate the end device production costs. Accordingly, if the critical lithography step could be used once for multiple layers rather than multiple times for each single layer, then the end device cost would roughly be reduced in proportion to the number of layers processed simultaneously.

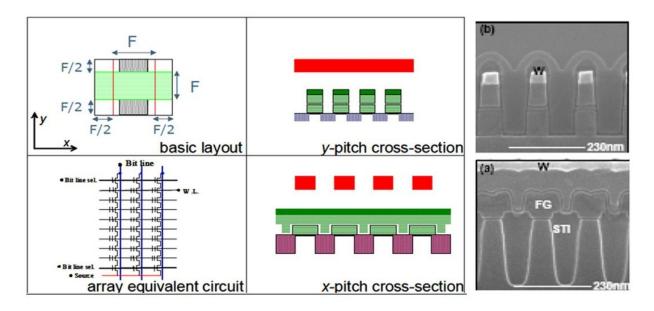

The first merchants to recognize this option and who are moving to monolithic 3D are the NAND Flash vendors, as illustrated in the next figure.

\*2011 Symposium on VLSI Technology Digest of Technical Papers Jungdal Choi and Kwang Soo Seol Semiconductor R&D Center, Samsung Electronics Co., Ltd.

The technical transition of NAND toward the 3D NVM era.

Using the proper architecture, multiple transistor layers could be processed together with a huge reduction in cost per layer. This could be applied to many different types of regular devices.

The following illustrates the concept applied to a floating-body DRAM:

**Process Flow: Step 6** Using methods similar to Steps 2-5, form multiple Si/SiO<sub>2</sub> layers, RTA

## Process Flow: Step 7 Use lithography and etch to define Silicon regions

Process Flow: Step 11

Construct BLs, then contacts to BLs, WLs and SLs at edges of memory array using methods in [Tanaka, et al., VLSI 2007]

The MonolithIC 3D Inc. website presents more details for such a <u>DRAM</u> flow, and also related flows for <u>RRAM</u> and <u>NAND Flash</u> memories.

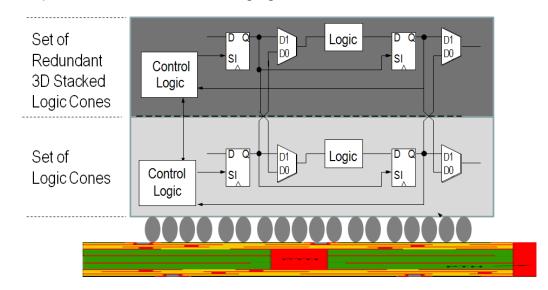

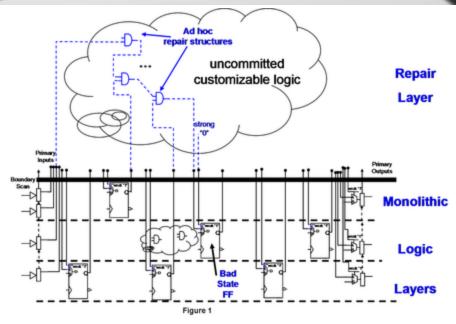

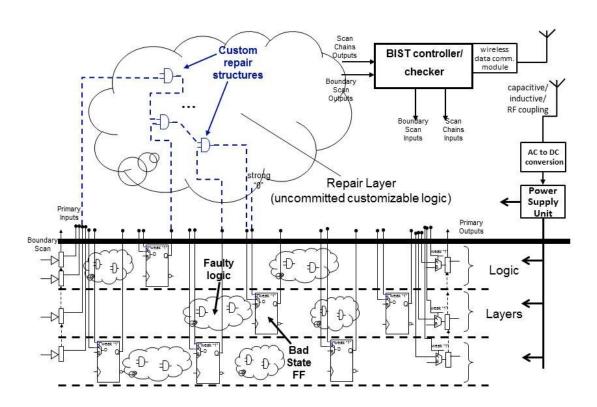

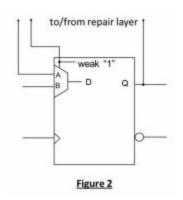

#### 6. Logic redundancy allowing 100x integration with good yield

The strongest value of an IC is the integration of many functions in one device. This is and will be the most important driver of Moore's Law because by integrating functions into one IC we achieve orders of magnitude benefits in power, speed, and costs. At any given technology node the limiting factor to integration is yield. As yield relates strongly to device area, most vendors are trying to limit the die size to about 50mm²-100 mm². Some product applications require an extremely large die of over 600mm², but those are rare (and high value-add) cases because the yield goes down exponentially as die size grows.

While memory redundancy is prevalent in the IC industry, logic redundancy is only used in a few FPGAs – no solution has been found after the failure of Trilogy, where "Triple Modular Redundancy" was employed systematically. Every logic gate and every flip-flop were triplicated with binary two-out-of-three voting at each flip-flop. Quoting Gene Amdahl: "Wafer scale integration will only work with 99.99% yield, which won't happen for 100 years." (Source: Wikipedia)

An additional advantage of monolithic 3D is the ability to construct redundancy for circuits including logic, with minimal impact on the design process and while maintaining circuit performance.

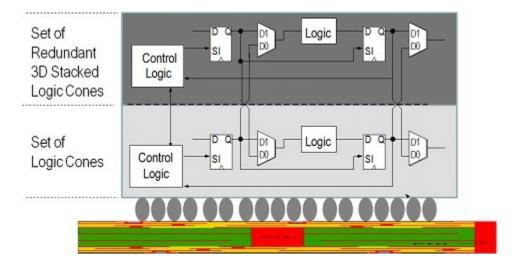

The concept is illustrated in the following figure:

There are three primary ideas here:

- > Swap at logic cone granularity.

- Redundant logic cone/block directly above, so no performance penalty.

- Negligible design effort, since the redundant layer is an exact copy.

The new concept leverages two important technology breakthroughs.

The first is the Scan Chain technology that enables a circuit test where faults are identified at the logic cone level. The second is the monolithic 3D IC which enables a fine-grained redundancy: replacement of a defective logic cone by the same logic cone that is only ~1 micron above.

Accordingly, by just building the same circuit twice, one on top of the other, with minimal overhead, every fault could be repaired by the replacement logic cone above. Such repair should have a negligible power penalty and a minimal cost penalty whenever the base circuit yield is about 50%. There should be almost no extra design cost and many additional benefits can be obtained.

This redundancy technique could be also used to repair faults throughout the device life-time, including in the field, which is a powerful advantage.

#### So the immediate question should be: how far can we go with such an approach?

A simple back-of-the-envelope calculation should start with the number of flipflops in a modern design. In today's designs we expect more than one million F/F (and their logic cones). Consequently, if we expect one defect, then a device with redundancy layer would work unless the same cone is faulty on both layers, which probability-wise would be one in a million!

Clearly we have removed yield as a constraint to super-scale integration. We could even integrate 1,000 such devices!!!

The ultra-integration value could be as much as:

- ~10X Advantage of 3D WSI vs. 2D @ Board Level

- ~10X Advantage of 3D WSI vs. 2D @ Rack Level

- > ~10X Advantage of 3D WSI vs. 2D @ Server Farm Level

Overall, a ~1000x advantage is possible, all due to shorter wires. Instead of placing chips on different packages, boards and racks, we integrate on the same stacked chip.

#### 7. Modular Platform

The 3D monolithic device would be a good fit to platform-based designs wherein some part of the device is used by all customers and others are tailored to a specific market/customer segment as illustrated by the following figure.

Such a system architecture could be inexpensively used in many market segments and with multiple variations. An interesting one could be in the FPGA sector where the same platform could come with many flavors of memories and I/O.

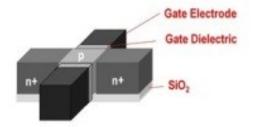

#### 8. Stacked layers are naturally SOI

The upper layer or layers of monolithic 3D devices are naturally Silicon-On-Insulator (SOI). The advantages of SOI are well-established, increase with scaling, and include:

- Near ideal sub-threshold swing

- Reduced device cross talk

- Lower junction leakage

- Effective back bias and multi-Vt options

- ➤ Multiple gate operation for superb electrostatic channel control

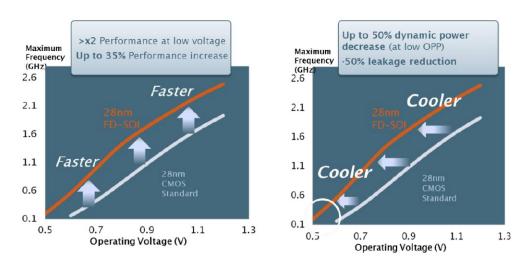

The recent developments of Fully Depleted SOI (FD-SOI) and SOI-FinFet has taken that advantage much further, and include:

- Lower manufacturing costs than bulk

- Less across-the-die transistor variation than bulk

Figure 8: FD-SOI: faster and cooler

Source: ST-Ericsson < http://www.stericsson.com/technologies/FD-SOI-eQuad-white-paper.pdf>

#### 9. Other ideas

There are other powerful advantages to monolithic 3D including those that we will discover in the future. In this chapter we present some specific applications where monolithic 3D provides significant advantages.

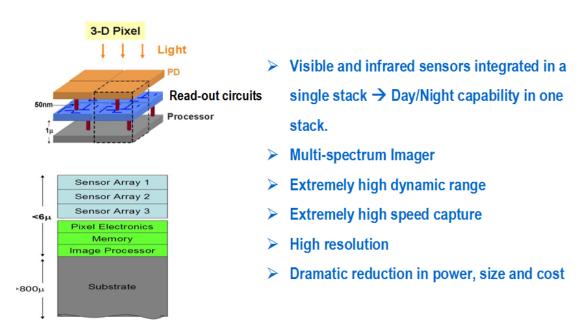

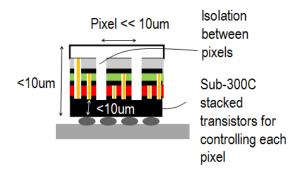

#### A. Image sensor with Pixel electronics

The image sensor industry has moved to back-side illumination to increase the image sensor area utilization. By adding the option for multiple layers many additional benefits could be gained as illustrated below:

An interesting option is to build the pixel electronics behind every pixel and provide a very high dynamic range by counting and resetting individual sensors.

#### B. Micro-display

The display market is always looking to reduce power and size while increasing the resolution and brightness. Monolithic 3D could provide ultra-high resolution with extreme power efficiency and minimal size, by combining drive electronics with layers of different color light emitting diodes as is illustrated below.

Can control color of light using feedback circuits in silicon layer

- ➤ A high-quality LED display without filters, polarizers, liquid crystals

- → Avoids size and power penalty of these components

- → 1/10<sup>th</sup> power, much less weight than standard LCD display

- → Brighter and more stable than OLED displays

- Can use as display, LED or communication device

#### 10. Summary

Monolithic 3D is a disruptive semiconductor technology. It builds on the existing infrastructure and know-how, and could bring to the high tech industry many more years of continuous progress. While it provides the advantages that dimensional scaling once provided, monolithic 3D offers many more options and benefits. And the best of all is that it could be done in conjunction with dimensional scaling.

Now that monolithic 3D is practical, it is time to augment dimensional scaling with monolithic 3D-IC scaling.

# Chapter 4 - How can 3D be cheaper? Isn't it twice the cost?

by Brian Cronquist, VP of Techology and IP of MonolithIC 3D Inc.

An old CEO (John East of Actel) of mine kept drilling into our heads that "faster, cheaper, and easier to use" was the path to success in the IC industry, and that "Cheaper" was the key element of those three. Economics has always been a, maybe even **the**, key driver for scaling in specific [Moore's 1995 SPIE speech] and the industry in general.

So it was no surprise that when I have brought 3D-IC, and specifically monolithic 3D, into the potential solution space for combating the growing only-nations-can-afford-them costs of conventional (Dennard, etc.) scaling [IBM: Scaling dead], the first question out of their mouths (or keyboards) is: "Hey, doesn't it cost twice as much to fold and stack it, so one gains nothing and perhaps even *loses* something due to the added costs of doing the 3D process (bonding, cleaving, connection)???" Well, when I started my monolithic 3D journey, I had the same first thoughts and questions. Here are a few of the answers....more will be forthcoming in future blogs and publications. Cost is a vast topic.

#### **Die Size/Cost**

"Hey, if I fold my chip over once, then I have the same silicon area (cost) as 2D but now double the processing, metal layers, etc., plus the costs of making and connecting the stack, right?" Well, that was my first impression too. But let's take a deeper look. By placing about half the circuitry above the other half (i.e.: "folding"), not only do the long wires get shorter, but so does the average wire\*. Hence, close to all of the logic gate to logic gate drivers and block to block buffers become smaller. Since they are smaller, then the circuitry moves closer to its neighbor; hence, the drivers can become smaller again. This *positive feedback mechanism* has been modeled by many people. Take a look at Davis, Zhou, and Synopsys, the references can be found at [Refs] as well as Meindl at MCISE 2003. This is a tractable problem for the universities, so there are many studies out there.

At Monolithic 3D Inc., we also have taken a close look at this to convince ourselves. Deepak took an older version of the IntSim tool he developed as part of his PhD thesis at Georgia Tech [Refs] and upgraded it to 3D. You will see more

publications on this tool and results, and it will soon be available on our website for you to try [3DSim]. Here is one result: The baseline was a 600MHz low power 2D logic core constructed at 22nm. A more complete description is at [Why Monolithic 3D], but the bottom line is: The monolithic 3D IC footprint is one fourth the die size of the 2D, and the total silicon area of the 3D chip is slightly less than half of the 2D chip (24 sq. mm vs 50 sq. mm).

| 22nm node                      | 2D-IC             | 3D-IC<br>2 Device Layers | Comments                              |

|--------------------------------|-------------------|--------------------------|---------------------------------------|

| Frequency                      | 600MHz            | 600MHz                   |                                       |

| Metal Levels                   | 10                | 10                       |                                       |

| Average Wire Length            | 6um               | 3.1um                    |                                       |

| Av. Gate Size                  | 6 W/L             | 3 W/L                    | Since less wire capacitance to drive  |

| Die Size (active silicon area) | 50mm <sup>2</sup> | 24mm²                    | 3D-IC → footprint 12mm²               |

| Power                          | Logic = 0.21W     | Logic = 0.1W             | Due to smaller Gate Size              |

|                                | Reps. = 0.17W     | Reps. = 0.04W            | Due to shorter wires                  |

|                                | Wires = 0.87W     | Wires = 0.44W            | Due to shorter wires                  |

|                                | Clock = 0.33W     | Clock = 0.19W            | Due to less wire capacitance to drive |

|                                | Total = 1.6W      | Total = 0.8W             |                                       |

3D with 2 device layers → 2x power reduction, ~2x active silicon area reduction vs. 2D

Looks a lot like one nodal scale.....

But what about the added costs to bond, cleave, connect? See the next section...litho drives the wafer processing costs, mostly due to depreciation load. The strata to strata connect is only a 1 max 2 litho step adder to the 2x40+ total, using the same tools as a regular via.

#### **Capital/Depreciation Cost**

The majority of the cost of a die, assuming one is at yield maturity, is driven by the depreciation of the capital. The major capital cost of the modern wafer fab is the litho tools. And we all see the increasing costs and fears in this area <u>Litho EETimes</u>...100M\$+ for a EUV machine <u>EUV Cost</u>. Also, as an old *fab-rat* and foundry guy, I can immediately relate to the fear many fab mangers and foundry execs have when they see the IBS trend [IBS 2010] and the ASML/AMAT price lists: How can I

keep up? Well, as explained by Israel a few blogs ago [Israel] by scaling UP with 3D and hence using the same litho tools, etc. to make the 3D stack, the wafer cost becomes much cheaper than the scale down wafer, the scale down wafer being subject to new litho tool process and depreciation cost. For monolithic 3D the only incremental capital would be for the wafer bonder/cleaving, implanter, and CMP machines, which are in the single digit M\$ per machine costs, not the triple digit M\$ per copy of NGL. The strata to strata via connect will look and act and process like a regular inter-metal via. We will be detailing this in upcoming publications, utilizing the Sematech COO framework.

Lots more to talk about (like lower mask costs), but I'll stop here for now. It's a big area. Ripe for many savings, and, like anything new, has the potential for unforeseen costs too....yes, yield and repair/redundancy mitigations will be a future subject. When you have a paradigm shift, as Zvi talked about last week [Zvi] and Deepak talked about in Monday's blog [Deepak], there can be many interesting opportunities to make chips faster, better, and cheaper....

What are YOUR questions and comments about 3DIC and cost? What do you think?

One more thinking question, especially for those who have *not* **lived** *in* a wafer fab (yup, I had a cot behind the diffusion furnaces when we started CSM Fab-1): With all the 'goodness" promised by 3DIC, doesn't it make sense to put 3D into the well-known and proven batch economics of the wafer fab?

\*This is one of the key differences between TSV 3DIC and monolithic 3DIC: The long wires get shorter for both, but the remainder and greater number of wires only get shorter for the Monolithic 3D case due to vertical connectivity being approximately equal to horizontal connectivity.

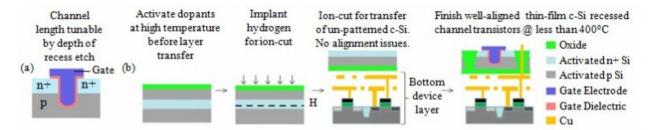

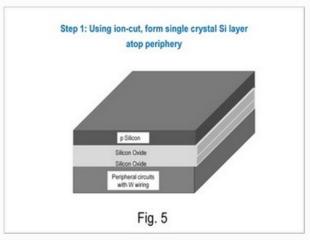

# Chapter 5 - Obtaining Monocrystalline Semiconductor Layers for Monolithic 3D

by Israel Beinglass, CTO of MonolithIC 3D Inc.

The idea of Monolithic 3D where several layers of devices are built, has been around for a few years. Many approaches were taken to create one or several layers of transistors on a completed first device (Transistor and interconnect).

Saraswat in <a href="www.jbkempf.com/~jb/Post-CMOS/Stanford/Saraswat.ppt">www.jbkempf.com/~jb/Post-CMOS/Stanford/Saraswat.ppt</a> depicted the concept of multilayer Monolithic 3D with several "transistor levels" (Figure 1). Furthermore, he suggested to 1.nucleate and 2.crystallize amorphous silicon, forming the second level of transistors followed by another set of interconnect layers (Figure 2). Nucleating and crystallizing amorphous silicon turns to be a very difficult task especially when the chip has millions of transistors per level and when elevating the temperature could be detrimental. An alternative way is using TFTs on the second level of silicon, the problem with that is of course very poor performance of the transistors even after crystallization of the amorphous silicon to polycrystalline materials, as well as the need to generate S/D junctions at high temperature that will adversely affect the underlying devices.

Figure 1

Figure 2

Another way which was suggested is low temperature Ge epitaxial over growth from "windows" in the silicon substrate and laser annealing the structure (Figure 3). This technology was developed by P. Griffin from Stanford and graduate students J. Feng,

#### M. Kobayashi and G. Thareja

(http://nanodevice.stanford.edu/3dworkshop/docs/8 Griffin-

<u>TEL3DWorkshopNov07.pdf</u>). They reported some limited success on growing epitaxial Ge. However fully integrating the technology seems to run into insurmountable difficulties of process control, as well as integrating Ge transistors on a full advanced CMOS process.

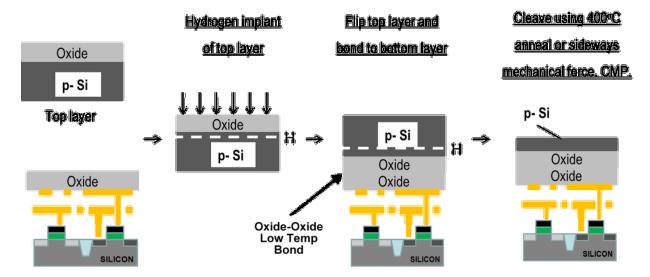

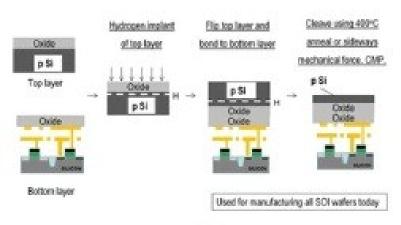

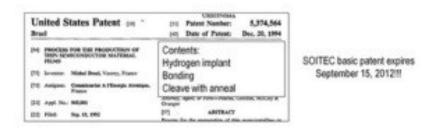

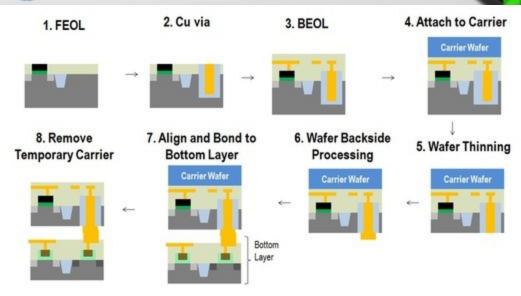

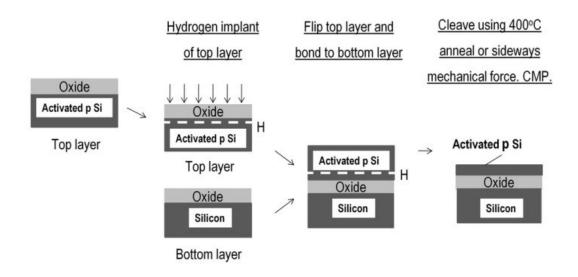

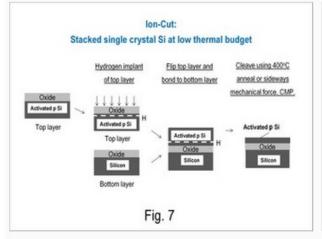

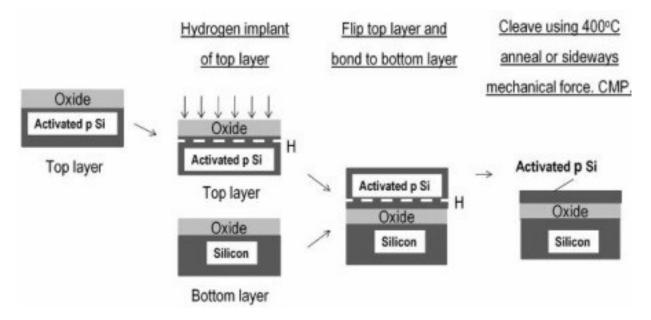

The other approach is integrating thin layer transfer onto a fully processed wafer, by that creating a second level of transistors, followed by a set of interconnect layers. The layer transfer is similar to the "smart-cut" process described by SOITEC in <a href="http://www.soitec.com/pdf/SmartCut\_WP.pdf">http://www.soitec.com/pdf/SmartCut\_WP.pdf</a> (Figure 4).

Applying layer transfer technology along with MonolithIC 3D Inc.'s IP portfolio is a new

Figure 3

Initial silicon waters A & B

Oxidation of water A to create involating layer

Saunt Cut ion implantation indoes formation of an in-depth weakmed layer

Cleaning & bonding water A to the handle subotrate, water B

Saunt Cut - cleavage at the mean ion penetration depth uplan off water A

Water B water B

Smart Cut - cleavage at the mean ion penetration depth uplan off water A

Water B water B

Smart Cut - cleavage at the mean ion penetration depth uplan off water A

Water B water B

Smart Cut - cleavage at the mean ion penetration depth uplan off water A

Smart Cut - cleavage at the mean ion penetration depth uplan off water A

Water B Water B

A

Water B

Smart Cut - cleavage at the mean ion penetration depth uplan off water A

New A

New B

Figure 4

and fresh way to build the next generation of 3D device integration.

### **Chapter 6 - Low Temperature Cleaving**

by Brian Cronquist, VP of Technology and IP of MonolithIC 3D Inc.

Thanks to everybody who came by our booth at SemiconWest <u>SemiconWest</u> <u>2012</u> this second year! We really enjoyed talking with you about all the exciting possibilities for new products and processes that are enabled by monolithic 3D IC.

For those who could not make it, here is what our booth looked like:

Nice tie again Zvi! You can still visit us at <a href="https://www.monolithic3d.com">www.monolithic3d.com</a>.

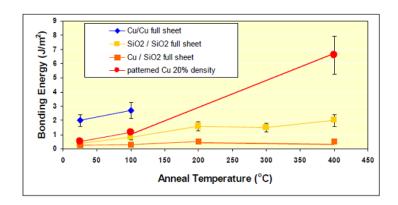

The most common area that you asked us was about low temperature (less than 400°C) bonding and low temperature cleaving processes. The two topics are quite interrelated: One must make the bond stronger than the energy it takes to cleave at the plane you want, rather than cleave at th at fresh bond. In October last year I wrote a blog about the many low temperature bonding techniques and strategies available and their respective bond strengths. Today, I would like to briefly address some of the low temperature cleaving methods available. Generally they involve either a mechanically induced (blade, gas jet, water jet) method, a lower temp thermal (co-implantation, microwave, etc.) cleaving/layer-transfer method, or a combination of both.

Here are a few papers, with some industrial announcements at the end.

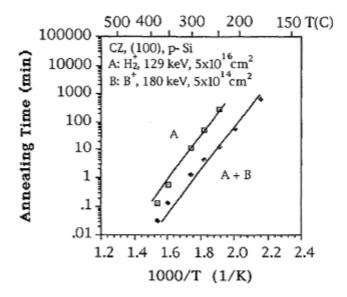

One of the earliest methods published is co-implantation by Q.Y. Tong et al. of Duke University at the 1997 IEEE SOI Conference. Tong could greatly affect the kinetics of the hydrogen blister formation by co-implantation of Boron. They were able to transfer a 0.4um silicon layer onto a quartz substrate with a 150°C exposure to the quartz by pre-annealing the co-implanted silicon for 10 minutes at 250°C.

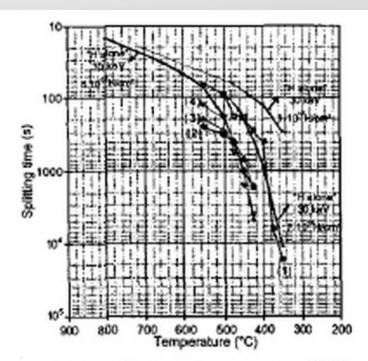

Fig. 1 B+H co-implant effect on times required to form optically detectable surface blisters in hydrogen implanted Si as a function of annealing temperature

<u>Tong</u> with colleagues at the Max-Planck-Institute followed up with more co-implantation

FIG. 1. Time required to form H implantation-induced optically detectable surface blisters on H-implanted, uniformly doped Si wafers (with phosphorous or boron concentrations as indicated) as a function of inverse absolute temperature.

kinetics data in a 2008 Applied Physics Letter. They again demonstrated a 200°C silicon cleave.

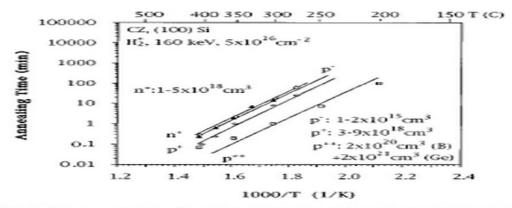

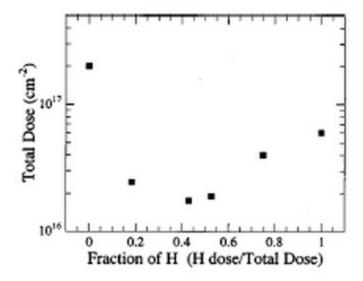

In 1998 App. Phys. Lett., Agarwal et al. showed that He implanted with the H could lead to a significant decrease in the total implant fluence (and hence cost) necessary to achieve Si layer transfer. The total implantation dose can be three times smaller than that which is necessary using H alone.

FIG. 2. Total (H<sup>+</sup> + He<sup>+</sup>) implantation dose necessary for blistering as a function of the fraction that is H<sup>+</sup>.

<u>Nguyen et al.</u> of Soitech/CEA-Leti, at the *2003 IEEE SOI Conference* showed that He co-implantation could be used to control the kinetics, so time, dose and temperature trades could be made.

Fig. 2: Splitting kinetics in the various cases of H/He coimplantation (1, 2, 3, 4) compared with cases of H implanted alone

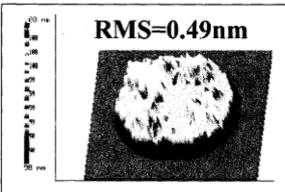

Ma, et al. showed in Semcond Sci. Technol. 2006 that a co-implanted cleave has a smoother surface than a hydrogen-only implanted cleave.

Table 1. The RMS surface roughness of SOI fabricated by B\*/H\* co-implantation and H\*-only implantation.

| Dose and energy of implantation                                                                                            | RMS surface<br>roughness |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Co-implantation: B*: 180 keV, 1 × 10 <sup>16</sup> cm <sup>-2</sup><br>H*: 60 keV, 4.5 × 10 <sup>16</sup> cm <sup>-2</sup> | 2.1 nm                   |

| H-only implantation: $H^*$ : 140 keV, $6 \times 10^{36}$ cm <sup>-2</sup>                                                  | >10 nm                   |

In 2000 App. Phys. Lett., <u>Henttinen et.al</u> showed mechanical cleaving, blade or N2 gas, on low temperature bonded silicon wafers (ox-ox bond). Depending on the H dose, Henttinen could

TABLE I. Effects of the hydrogen implantation dose and the bond annealing temperature on the mechanical exfoliation. The "+" sign denotes that the Si layer is successfully transferred, whereas the "-" sign indicates that the layer is not transferred. The bond annealing time is shown in parentheses.

|                     | Implantation dose (H <sub>2</sub> /cm <sup>2</sup> ) |          |           |

|---------------------|------------------------------------------------------|----------|-----------|

| Bonding temperature | 4.0×10 <sup>16</sup>                                 | 4.5×1016 | 5.0×1016  |

| 200 °C              | -(2 h)                                               | -(2 h)   | +(2 h)    |

| 250 °C              | -(2 h)                                               | +(2 h)   | +(30 min) |

| 300 °C              | +(2 h)                                               | +(2 h)   | +(2 h)    |

cleave the silicon wafers at 200°C or 300°C. <u>Henttinen et.al</u> followed up later in 2002 in *J. Nucl. Instr. and Meth. in Phys* with fundamental mechanistic studies and also demonstrated that with enough B doping one can enable H-implanted layer exfoliation below 200°C.

Cho et al., in 2003 App. Phys. Lett. reported that full wafer layer transfer could be achieved with a mechanical cleave (edge initiated crack propagation) after a 250°C annealing that enabled the bonding strength at the acceptor/donor interface to exceed the required cleave energy at the hydrogen implant plane.

<u>En, et al.</u>, of Silicon Genesis, described a room temperature H implant using PLAD (Plasma Immersion Ion Implantation), plasma assisted oxide to oxide bonding, and a room temperature mechanical cleave process at the *1998 IEEE SOI Conference*.

Figure 3: Thin-film measurement of an 8-inch SOI overlayer. Silicon overlayer thickness is 99nm and thickness non-uniformity range (6-sigma) is 2.7 nm with a 4mm edge exclusion

Table 1: PIII machine specifications

| Spec Description           | Spec Value               |

|----------------------------|--------------------------|

| Wafer Size                 | 4"-12"                   |

| Implant Time               | 60-120s                  |

|                            | (wafer size independent) |

| Area energy non-uniformity | +/- 5% range             |

| Area dose non-uniformity   | +/- 10% range            |

Table 2: Genesis Process SOI wafer specifications

| Spec Description              | Spec Value                       |

|-------------------------------|----------------------------------|

| Wafer Size                    | 4"-12"                           |

| SOI layer thickness (tSOI)    | 50-250nm                         |

| tSOI uniformity               | < 3nm range                      |

| Buried oxide thickness (tBOX) | No restrictions                  |

| tBOX uniformity               | < 3% range                       |

| Surface roughness             | < 1.5A R <sub>cms</sub> (2x2 μm) |

<u>Current, et al.</u> of Silicon Genesis, showed a wafer separation tool in *MRS 2001* where they utilized a pressurized N2 jet to cleave silicon bonded pairs at room temperature.

Recently from the industrial side:

Soitec announced at SemiconWest 2012 the availability of a room temperature smart cut:

"Soitec's low-temperature Smart Cut process uses oxide-oxide molecular bonding and atomic-level cleaving to transfer mono-crystalline silicon films as thin as 0.1 micron onto partially or fully processed wafers. On this new material layer, a second level of devices can be processed and this integration can be repeated in an iterative mode. Transferring an extremely thin layer enables higher interconnect density, higher signal throughput and simpler TSV processing. Benefits include increased computing bandwidth, lower overall manufacturing cost, and power savings due to the reduced wiring distance between connected devices. This final benefit is well suited for producing advanced memory or CMOS logic 3D IC systems." See: http://www.soitec.com/en/news/press-releases/article-346/

SiGen (Silicon Genesis) has tools (some shown above) available that will bond and cleave at or near room temperature: <a href="http://www.sigen.net/semi">http://www.sigen.net/semi</a> debondCleave.html

#### References:

TONG, Q.-Y., et al., "Low Temperature Si Layer Splitting", Proceedings 1997 IEEE International SOI Conference, Oct. 1997, pp. 126-127

TONG, Q.-Y., et al., "A "smarter-cut" approach to low temperature silicon layer transfer", Applied Physics Letters, Vol. 72, No. 1, 5 January 1998, pp. 49-51

AGARWAL, A., et al., "Efficient production of silicon-on-insulator films by co-implantation of He+ with H+" Applied Physics Letters, vol. 72, no. 9, March 1998, pp. 1086-1088.

NGUYEN, P., et al., "Systematic study of the splitting kinetic of H/He co-implanted substrate", SOI Conference, 2003, pp. 132-134

MA, X., et al., "A high-quality SOI structure fabricated by low-temperature technology with B+/H+ co-implantation and plasma bonding", Semiconductor Science and Technology, Vol., 21, 2006, pp. 959-963

HENTTINEN, K. et al., "Mechanically Induced Si Layer Transfer in Hydrogen-Implanted Si Wafers," Applied Physics Letters, April 24, 2000, p. 2370-2372, Vol. 76, No. 17.

HENTTINEN, K. et al., "Cold ion-cutting of hydrogen implanted Si," J. Nucl. Instr. and Meth. in Phys. Res. B, 2002, pp. 761-766, Vol. 190.

CHO, Y., et al., "Low Temperature Si Layer Transfer by Direct Bonding and Mechanical Ion Cut," Applied Physics. Letters., vol. 83, no. 18, November 2003, pp. 3827-3829.

EN, W. G., et al., "The Genesis ProcessTM: A New SOI wafer fabrication method", Proceedings 1998 IEEE International SOI Conference, pp. 163-164 (Oct. 1998).

CURRENT, M. I., et al., "Atomic-layer Cleaving and Non-contact Thinning and Thickening for Fabrication of Laminated electronic and Photonic Materials", 2001 Materials Research Society Meeting, April 16-20 2001, Paper I8.3.

### **Chapter 7 - Low Temperature Wafer Direct Bonding**

by Brian Cronquist, VP of Technology and IP of MonolithIC 3D Inc.

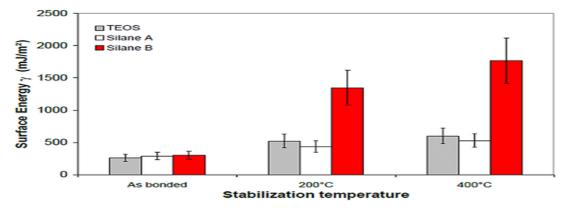

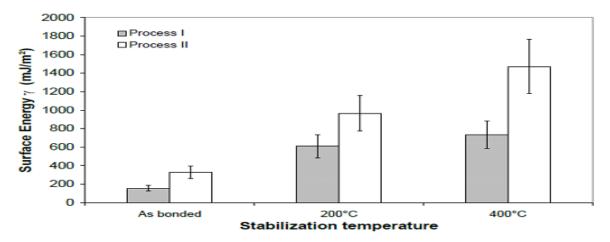

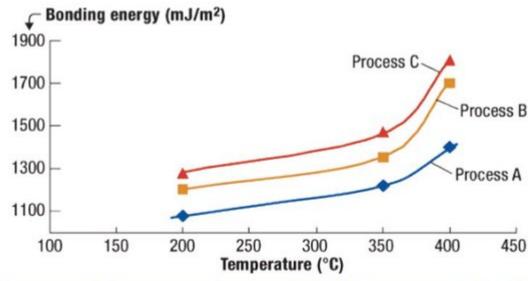

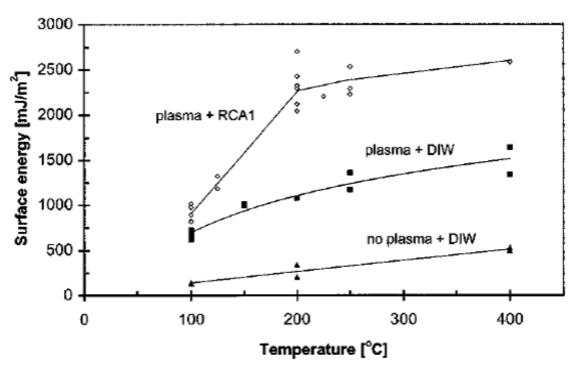

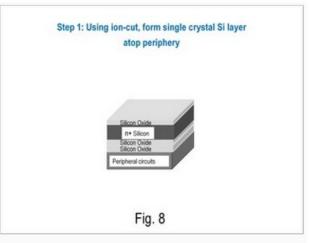

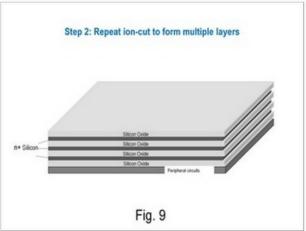

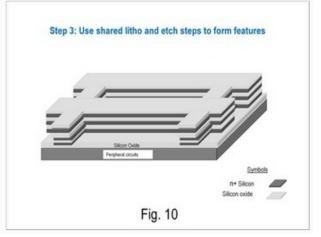

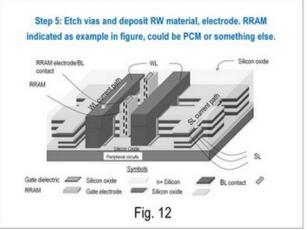

Sometimes we get questions about a particular aspect of the monolithic 3DIC flow. Here I would like to talk about Low Temperature Wafer Direct Bonding, where an important concern is the strength of the wafer to wafer oxide to oxide bond. Can it survive the subsequent transistor formation or wafer thinning processing, whether that processing entails the shear forces of a CMP, the thermal gradients of a low temperature deposition, or the stress release of a plasma or wet etch?