# CMOS technologies: Our most power efficient solution today and our vision toward 10nm node and beyond

Maud Vinet, Advanced CMOS manager

## **Device technology roadmap**

Evolutionary scaling: technology driven performance improvement Early material and process 28FDSOI 10FDSOI 14FDSOI coupling Non planar/trigate/NW **FinFET High mobility materials** 10nm 28nm 5nm **14nm** 7nm **Disruptive scaling Steep slope devices Hybrid logic Mechanical** switches Alternative to scaling **Single Electron Transistor** Monolithic3D - M3D Early design coupling

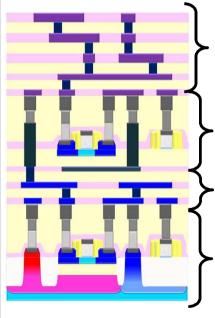

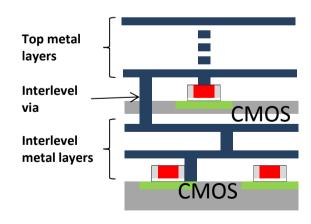

## **Monolithic 3D**

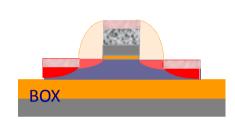

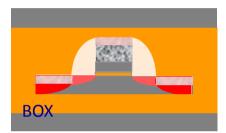

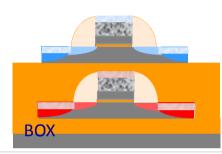

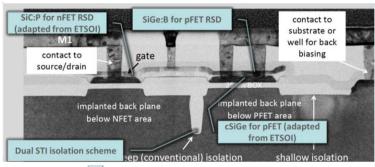

**Bottom transistor**

Top film realization

Top transistor

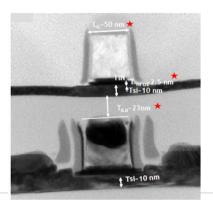

Lithographic alignement precision between stacked layers

- 14 M3D PDK available

- Based on CMOS/CMOS silicon demonstration

**Back-end**

**Upper level:**

Front-end + middle-end

Inter-level metal

Lower level:

Front-end + middle-end

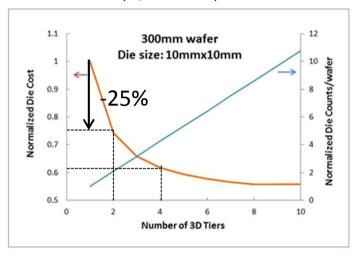

## **Interest for M3D**

Source: G. Bartlett, Global Foundries, SMC 2013

Without scaling avoid fab and process costs increase

Source: R. Gilmore, Qualcomm VP, ESSIRC 2012

Stack 2 layers: 25% die cost reduction

Average gain benchmark for 6 circuits/planar 1 node gain without scaling

3 metal levels

## **Technological ecosystem**

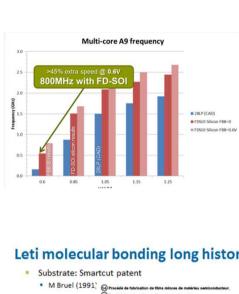

#### Leti molecular bonding long history

Smartcut based substrates

IC transfer by moelcular bonding

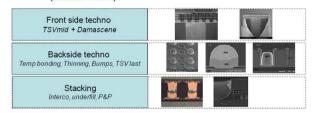

#### Leti 3D Integration platform

A complete and mature set of processes dedicated to 3D integration

Core 3D Technology (200mm & 300mm)

#### WIOMING: Wide I/O demonstrator (June 2012)

- Wide IO Memory Interface Next Generation

- Cooperation with STMicroelectronics, ST-Ericsson and

# Device technology roadmap

- Evolutionary scenario: nanowires and stacked nanowires as

- Disruptive scenario

- Steep slope device

- Mechanical switches

- SET/SAT as elements for a "disruptive" scenario

- Monolithic 3D for an "end of scaling" scenario:

- CMOS/CMOS for density

- N over P for co-integration of alternative channel materials

- New architectures like "memory in logic" and "neuromorphic"

- Resistive memories replacing charge based